Contract number: ITEA2 - 10039

# Safe Automotive soFtware architEcture (SAFE)

#### **ITEA Roadmap application domains:**

Major: Services, Systems & Software Creation

Minor: Society

## ITEA Roadmap technology categories:

Major: Systems Engineering & Software Engineering

Minor 1: Engineering Process Support

# WP3

# Deliverable D331a2: Proposal for extension of metamodel for error failure and propagation analysis

Due date of deliverable: 31/12/13

Actual submission date: 18/12/13

Project coordinator name: Stefan Voget

Organization name of lead contractor for this deliverable: Valeo

Editor: Florent Meurville (florent.meurville@valeo.com)

Contributors: Philippe Cuenot (Continental); Loic Quéran (Dassaut System); Andreas Baumgart (OFFIS); Markus Oertel (OFFIS); Tilman Ochs (BMW CAR IT); Christoph Ainhauser (BMW CAR

IT); Lukas Bulwahn (BMW CAR IT)

Reviewers: All WT3.3.1 Partners

# Revision chart and history log

| Version | Date       | Reason                                                                             |

|---------|------------|------------------------------------------------------------------------------------|

| 0.1     | 27/11/2013 | BMW Car IT update of section 10, Introduction of section 11.2, 11.3, 11.5 and 11.6 |

| 0.2     | 05.12.2013 | Conti-F review, updated of Section 11.7 and remove of Annex B                      |

| 0. 3    | 11/12/2013 | OFFIS update                                                                       |

| 0.4     | 13/12/2013 | Valeo correction + AltaRica new example provided                                   |

| 0.5     | 17/12/2013 | BMW CAR IT corrections                                                             |

| 0.6     | 18/12/2013 | Ready for release proposal                                                         |

| 1.0     | 18/12/2013 | Released                                                                           |

© 2013 The SAFE Consortium 2 (114)

# 1 Table of contents

| 4      | <b>-</b> |                                                                                                        | •  |

|--------|----------|--------------------------------------------------------------------------------------------------------|----|

| 1      |          | f contents                                                                                             |    |

| 2      |          | igures                                                                                                 |    |

| 3      |          | ablesve Summary                                                                                        |    |

| 4<br>5 |          | of WT 3.3.1 and structure of the document                                                              |    |

|        | -        | cope of WT 3.3.1                                                                                       |    |

|        |          | tructure of the document                                                                               |    |

| 6      |          | 262 concepts addressed by WT3.3.1 to evaluate risk of malfunctioning behavior                          |    |

|        |          | hort Overview of ISO26262 Chapters of interest for WT3.3.1                                             |    |

|        |          | 6026262 and General concept of Fault / Error / Failure for malfunctioning behavior and its propagation |    |

|        |          | ypes of Safety Analyzes recommended by ISO26262                                                        |    |

|        | -        | onsidered safety analyzes in WT3.3.1 (D331b)                                                           |    |

|        | 6.4.1    | Criteria-based assessment of most relevant safety analyzes methods using criteria                      |    |

|        | 6.4.2    | Final choice for D331b                                                                                 |    |

| 7      | -        | natic of evaluating malfunctioning behavior in distributed developments                                |    |

|        |          | ustration through an example                                                                           |    |

|        |          | ontracts Approach in distributed developments                                                          |    |

|        | 7.2.1    | Contracts Historical background                                                                        |    |

|        | 7.2.2    | Contracts basic description                                                                            |    |

|        | 7.2.3    | Contracts basic elements                                                                               |    |

|        | 7.2.4    | Contracts Failure Description                                                                          |    |

|        | 7.2.5    | Contracts Example                                                                                      |    |

|        | 7.2.6    | Contracts and Loop management                                                                          |    |

|        | 7.2.7    | Contracts and failure propagation mitigation with safety mechanism                                     |    |

|        | 7.2.8    | Conclusions on Contracts                                                                               |    |

| 8      | Fault ar | nd Propagation language overview and considered method in WT3.3.1                                      | 29 |

|        | 8.1 Hi   | iP-HOPS                                                                                                | 29 |

|        | 8.1.1    | HiP-HOPS Historical background                                                                         | 29 |

|        | 8.1.2    | HiP-HOPS basic description                                                                             | 29 |

|        | 8.1.3    | HiP-HOPS basic elements                                                                                | 31 |

|        | 8.1.4    | HiP-HOPS Failure Description                                                                           | 32 |

|        | 8.1.5    | HiP-HOPS Example                                                                                       | 34 |

|        | 8.1.6    | HiP-HOPS and loops management                                                                          | 34 |

|        | 8.1.7    | HiP-HOPS and failure propagation mitigation with safety mechanisms                                     | 36 |

|        | 8.1.8    | HiP-HOPS and ISO26262                                                                                  | 37 |

|        | 8.1.9    | EAST-ADL2 experiment with HiP-HOPS, limits and opportunities identified                                | 37 |

|        | 8.1.10   | Conclusions on HiP-HOPS                                                                                | 38 |

|        | 8.2 AI   | taRica                                                                                                 | 39 |

|        | 8.2.1    | AltaRica Historical background                                                                         | 39 |

|        | 8.2.2    | AltaRica basic description                                                                             | 39 |

|        | 8.2.3    | AltaRica basic elements                                                                                | 40 |

|        | 8.2.4    | AltaRica Failure Description and propagation                                                           | 41 |

|    | 8.2.5  | AltaRica Example                                                                   | 43  |

|----|--------|------------------------------------------------------------------------------------|-----|

|    | 8.2.6  | AltaRica and Loop management                                                       | 44  |

|    | 8.2.7  | AltaRica and failure propagation mitigation with safety mechanism                  | 45  |

|    | 8.2.8  | AltaRica and ISO26262                                                              | 47  |

|    | 8.2.9  | AltaRica concepts versus EAST-ADLV2.1                                              | 48  |

|    | 8.2.10 | AltaRica limits                                                                    | 49  |

|    | 8.2.11 | Conclusions on AltaRica                                                            | 49  |

| 8  | 3.3 C  | Prientation taken by WT3.3.1 in SAFE                                               | 50  |

|    | 8.3.1  | Pros and cons analysis of HiP-HOPS and AltaRica languages                          | 50  |

|    | 8.3.2  | Language choice in WT3.3.1                                                         | 51  |

|    | 8.3.3  | General requirements for a simplified SAFE language                                | 52  |

|    | 8.3.4  | Hypothesis taken in WT3.3.1                                                        | 53  |

|    | 8.3.5  | Refined requirements for a simplified SAFE language                                | 53  |

| 9  | Perfor | ning Fault/failure and error propagation based on EAST-ADL V2.1                    | 54  |

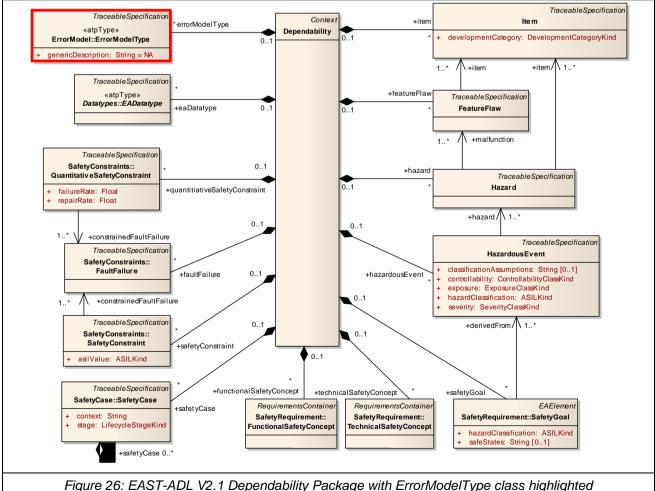

| g  | ).1 C  | Current state of EAST-ADL V2.1 concerning fault/failure and error propagation      | 54  |

| g  | ).2 A  | nalysis of Gap between EAST-ADLV2.1 ErrorModel and our needs                       | 57  |

| 10 | WT3.3  | .1 Contribution to SAFE Meta-Model                                                 | 59  |

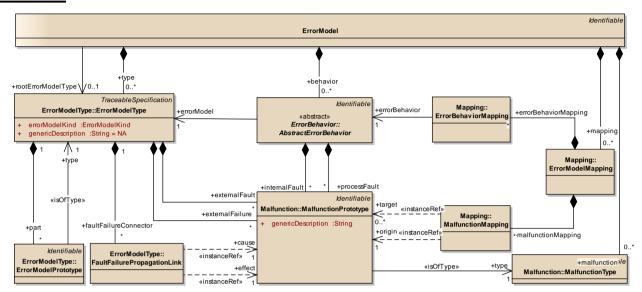

| 1  | 0.1    | Overview                                                                           | 59  |

| 1  | 0.2    | Petailed Description of Classes and Links                                          | 60  |

|    | 10.2.1 | ErrorModel                                                                         | 60  |

|    | 10.2.2 | ErrorBehavior                                                                      | 61  |

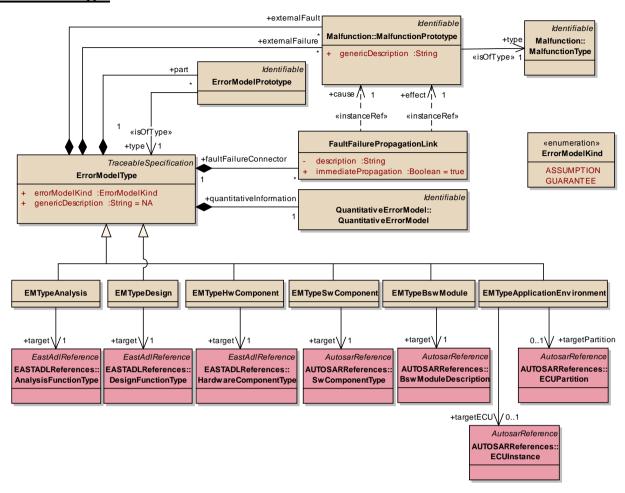

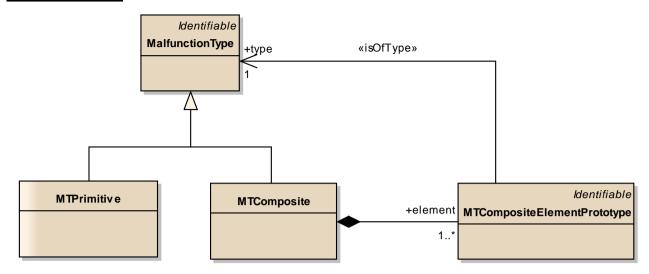

|    | 10.2.3 | ErrorModelType                                                                     | 64  |

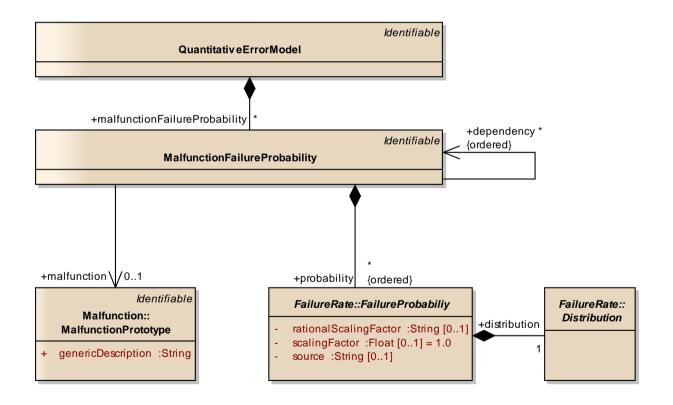

|    | 10.2.4 | QuantItativeErrorModel                                                             | 71  |

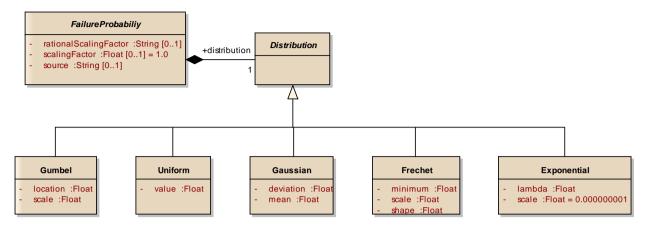

|    | 10.2.5 | FailureProbability                                                                 | 73  |

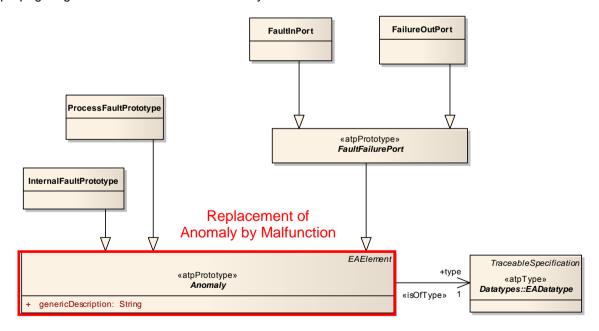

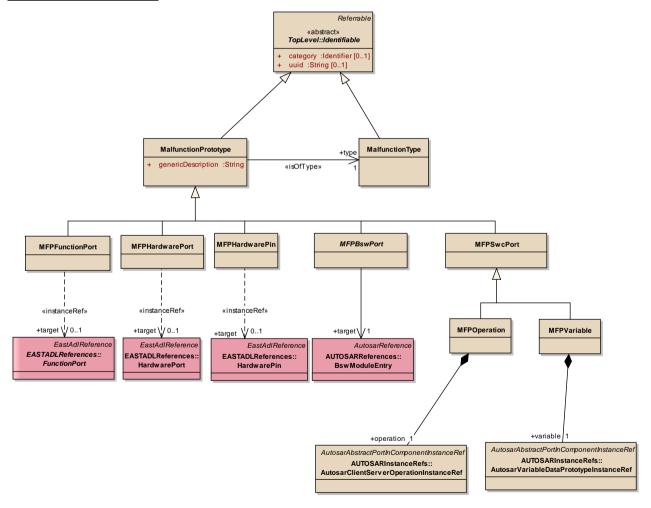

|    | 10.2.6 | Malfunction                                                                        | 75  |

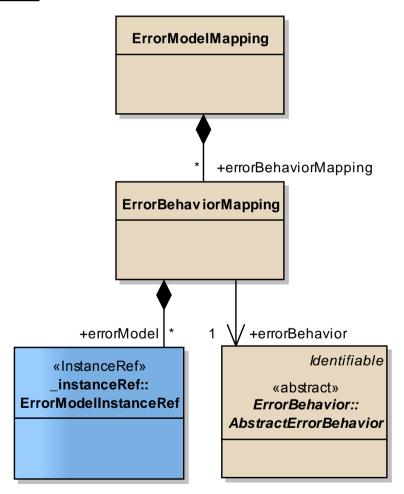

|    | 10.2.7 | Mapping                                                                            | 80  |

|    | 10.2.8 | _instanceRef                                                                       | 82  |

| 1  | 0.3 V  | VT3.3.1 Meta-model Description Based on an Example                                 | 88  |

| 11 | WT3.3  | .1 Error model Application Rules                                                   | 90  |

| 1  | 1.1    | system Model                                                                       | 90  |

| 1  | 1.2 F  | ailure probability of a single error                                               | 92  |

| 1  | 1.3 E  | rror model as Assumption or Guarantee                                              | 92  |

| 1  | 1.4 E  | rror model pattern 1 – Separation of application layer and application environment | 92  |

|    | 11.4.1 | Introduction                                                                       | 92  |

|    | 11.4.2 | Modeling approach                                                                  | 92  |

|    | 11.4.3 | Special case: horizontal error propagation prevented by application environment    | 94  |

|    | 11.4.4 | Error Model as Safety Contract                                                     | 95  |

|    | 11.4.5 | Modeling of Separation of Application Layer and Application Environment            | 95  |

| 1  | 1.5 E  | rror model pattern 2 – Quantitative Failure Analysis                               | 96  |

| 1  | 1.6 E  | rror Model pattern 3 - Independent failures, Error propagation probability         | 100 |

| 1  |        | rror model pattern 4 – Separation of Hardware and Software                         |     |

| 12 | Conclu | sions and next steps                                                               | 106 |

| 13 | Glossa | ry useful for D331a document                                                       | 107 |

| 14 | Abbrev | viations used in D331a document                                                    | 108 |

|    |        |                                                                                    |     |

| 15             | References                                                                                                                                                                                                             | .109         |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| [1]            | International Organization for Standardization: ISO 26262 Road vehicles - Functional safety. (2011)                                                                                                                    | .109         |

| [2]<br>http:/  | Project ATESST2: ATESST2 Partners. Review of relevant Safety Analysis Techniques, //www.atesst.org/home/liblocal/docs/ATESST2_Deliverable_D2.1_A3.2_V1.1.pdf                                                           | .109         |

| [3]            | http://www.itemuk.com/assets/docs/ToolKit_Manual.pdf                                                                                                                                                                   | .109         |

| [4]            | SPEEDS Consortium: SPEEDS Meta-model Syntax and Draft Semantics, D2.1c. (2007)                                                                                                                                         | .109         |

| [5]<br>D_SI    | Project CESAR: CESAR Partners. RE Language Definitions to formalize multi-criteria requirements V2, P2_R2.2_M2, http://www.cesarproject.eu/fileadmin/user_upload/CESAR_D_SP2_R2.2_M2_v1.000_PU.pdf                     | .109         |

| [6]<br>2009    | SPEEDS L-1 Meta-Model, SPEEDS WP2.1 Partners, SPEEDS Project Deliverable D2.1.5, Revision 1.0.1, May http://speeds.eu.com/downloads/SPEEDS_Meta-Model.pdf                                                              |              |

| [7]<br>Prog    | Hungar, H.: Compositionality with Strong Assumptions. In Proceedings of the 23 <sup>rd</sup> Nordic Workshop on gramming Theory. (2011) 19–21                                                                          | .109         |

| [8]<br>01-0    | Damm, W., Josko, B., Peikenkamp, T.: Contract based ISO CD 26262 safety analysis. SAE Technical Paper 20754, 2009, doi:10.4271/2009-01-0754 (2009)                                                                     |              |

| [9]<br>XML     | University of Hull, DRIS research group. The Definitive Guide to the HiP-HOPS XML Input File Format, HiP-HC Format.doc                                                                                                 |              |

| [10]<br>imple  | Yiannis Papadopoulos, Martin Walker, University of Hull "Qualitative temporal analysis: Towards a full ementation of the Fault tree Handbook", Control Engineering Practice, Vol.17 Issue 10, Elsevier Editions, 2009. | .109         |

| [11]<br>http:/ | Project ATESST2: ATESST2 Partners. EAST-ADL update suggestions for Safety Analysis support, //www.atesst.org/home/liblocal/docs/ATESST2_Deliverable_D3.1_A3.2_V1.1.1.pdf                                               | .109         |

| [12]<br>patte  | Yiannis Papadopoulos, Ian Wolfort, Martin Walker, University of Hull "Capture and Reuse of composable failerns", International Journal of Critical Computer Based Systems, Vol 1, Nos. 1/2/3 2010                      |              |

| [13]<br>thesi  | G. Point. AltaRica: Contribution à l'unification des methods formelles et de la Sûreté de fonctionnement. PhE is, Université Bordeaux 1, 2000.                                                                         |              |

| [14]<br>Publi  | A. Arnold, D. Bégay, and P.Crubillé. Construction and analysis of transition systems with MEC. World Scient ishers, 1994                                                                                               | ific<br>.109 |

| [15]<br>Relia  | A. Rauzy: A New Methodology to Handle Boolean Models with Loops In <i>IEEE Transactions on Reliability</i> . IE ability Society. Vol. 52, Num. 1, pp 96–105, 2003                                                      |              |

| [16]<br>Sûre   | T. Prosvirnova, and A. Rauzy: Système de Transitions Gardées : formalisme pivot de modélisation pour la té de Fonctionnement. In J.F. Barbet ed., <i>Actes du Congrès Lambda-Mu 18</i> . Octobre, 2012                 | .109         |

| [17]<br>syste  | Marc BOUISSOU: Gestion de la complexité dans les etudes quantitative de sûreté de fonctionnement de<br>ems. Collection EDF R&D aux éditions LAVOISIER*                                                                 | .109         |

| [18]<br>Supp   | Chen, D., Johansson, R., Lönn, H., Papadopoulos, Y., Sandberg, A., Törner, F., Törngren, M.: Modelling port for Design of Safety-Critical Automotive Embedded Systems. In: Proceedings of SAFECOMP (2008)              | .109         |

| [19]           | Safety Designer tool from Dassault System ; http://www.3ds.com/                                                                                                                                                        | .109         |

| [20]           | SIMFIA; http://www.apsys.eads.net/en/17/Software                                                                                                                                                                       | .109         |

| 16             | Acknowledgments                                                                                                                                                                                                        | .110         |

| 17             | Anney A: Manning hetween AltaRica and HiP.HOPS                                                                                                                                                                         | 111          |

© 2013 The SAFE Consortium 5 (114)

# 2 List of figures

| Figure 1: ISO26262 General Overview [1] highlighting where safety analyzes can help             | 11 |

|-------------------------------------------------------------------------------------------------|----|

| Figure 2: View of safety requirements refinement supported by safety analyses                   | 11 |

| Figure 3: Example of failures at ECU level which become faults at vehicle level                 |    |

| Figure 4: Example of a fault propagating to a hazard                                            |    |

| Figure 5: Example of RBD for 2 capacitors with several failure modes                            |    |

| Figure 6: Example of Preliminary Architecture of front lighting switch system                   |    |

| Figure 7: Example of requirements allocation from OEM to suppliers in a distributed development |    |

| Figure 8: Example of component perimeter known by a Tier 01 in distributed development          |    |

| Figure 9: SPEEDS Contract based specification of interface properties [4]                       | 22 |

| Figure 10: Virtual Integration of Heterogeneous Rich Components (HRC) [4]                       |    |

| Figure 11: Example of failure pattern                                                           |    |

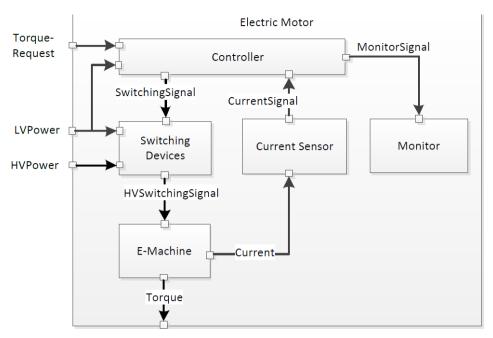

| Figure 12: Example an electric drive-train architecture                                         | 26 |

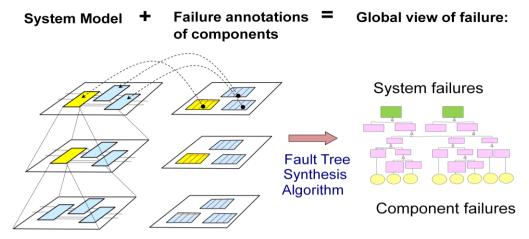

| Figure 13: HiP-HOPS methods overview for Fault Tree Synthesis                                   |    |

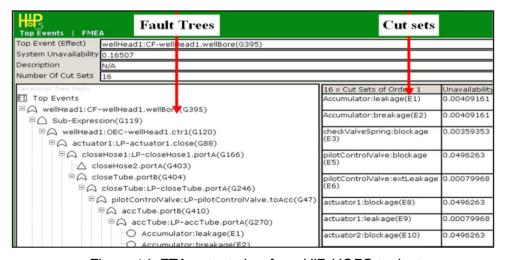

| Figure 14: FTA output view from HiP-HOPS toolset                                                |    |

| Figure 15: Loop example in HiP-HOPS                                                             |    |

| Figure 16: Loop example with diagnosis in HiP-HOPS                                              |    |

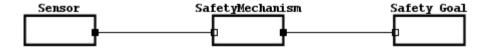

| Figure 17: Chain example with 5 links                                                           |    |

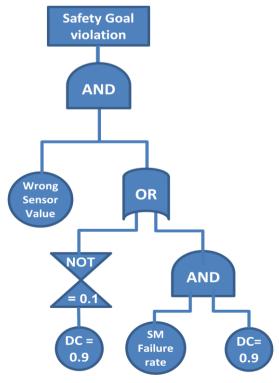

| Figure 18: HiP-HOPS example with Limp Home                                                      | 36 |

| Figure 19: ATESST2 HiP-HOPS versus EAST-ADLV2 mapping [11]                                      |    |

| Figure 20: Example of equivalence between if-then-else expressions and case expression          | 42 |

| Figure 21: AltaRica Code Example for our Valve                                                  | 43 |

| Figure 22: Example of safety mechanism modeled in Safety Designer                               | 45 |

| Figure 23: AltaRica Code Example for a safety mechanism                                         | 46 |

| Figure 24: FTA generation by Safety Designer [19] from AltaRIca complete model                  | 46 |

| Figure 25: SAFE language proposal                                                               | 51 |

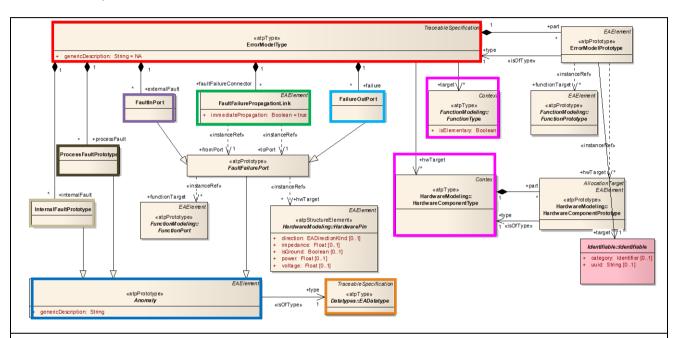

| Figure 26: EAST-ADL V2.1 Dependability Package with ErrorModelType class highlighted            | 54 |

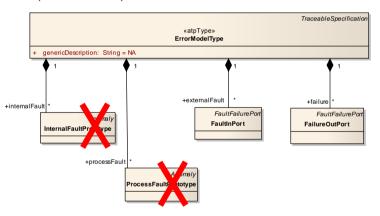

| Figure 27: EAST-ADLV2.1 ErrorModelType Content                                                  | 55 |

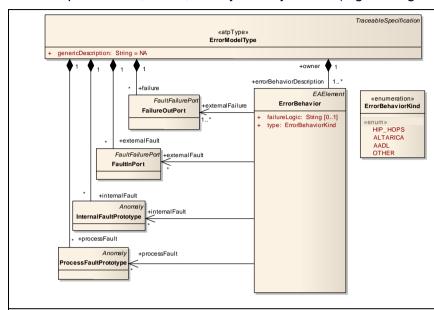

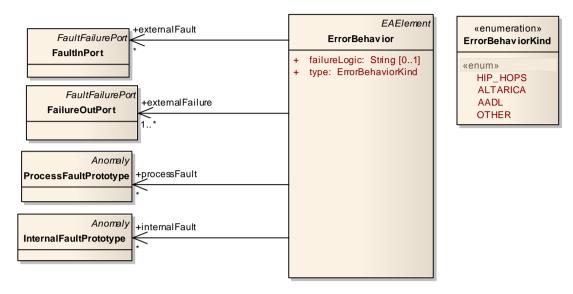

| Figure 28: EAST-ADLV2.1 ErrorBehavior Content                                                   | 56 |

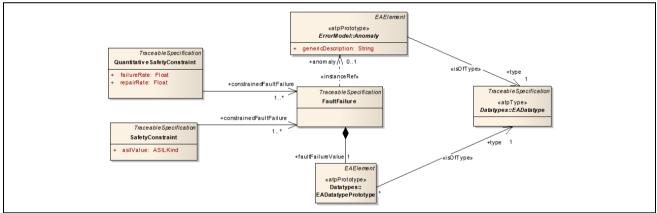

| Figure 29: EAST-ADLV2.1 FaultFailure Content                                                    | 56 |

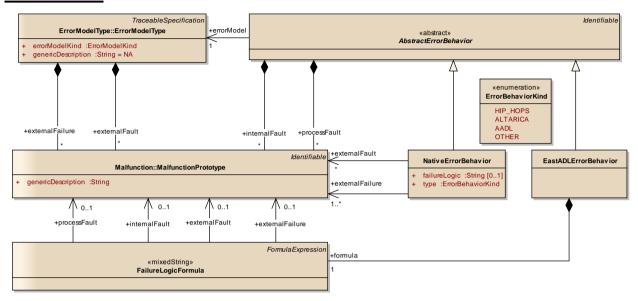

| Figure 30 : Overview of WT3.3.1 ErrorModel Package proposal                                     | 60 |

| Figure 31 : WT3.3.1 ErrorBehavior proposal                                                      | 61 |

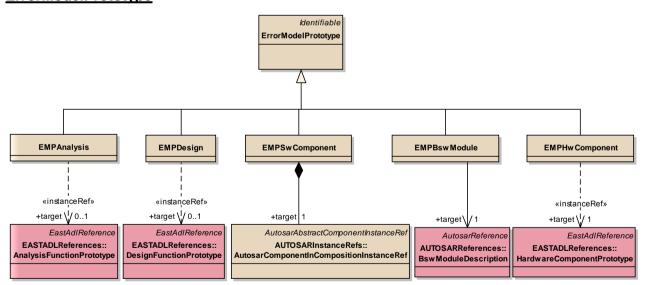

| Figure 32 : WT3.3.1 ErrorModelPrototype proposal                                                | 64 |

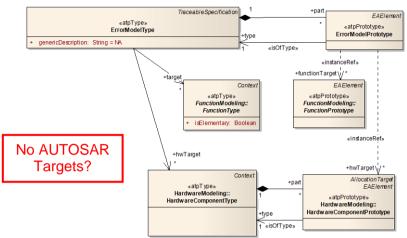

| Figure 33 : WT3.3.1 ErrorModelType proposal                                                     | 65 |

| Figure 34 : WT3.3.1 QuantitativeErrorModel proposal                                             | 71 |

| Figure 35 : WT3.3.1 FailureProbability proposal                                                 | 73 |

| Figure 36 : WT3.3.1 MalfunctionPrototype proposal                                               | 75 |

| Figure 37 : WT3.3.1 MalfunctionType proposal                                                    |    |

| Figure 38 : WT3.3.1 ErrorBehvaiorMapping proposal                                               | 80 |

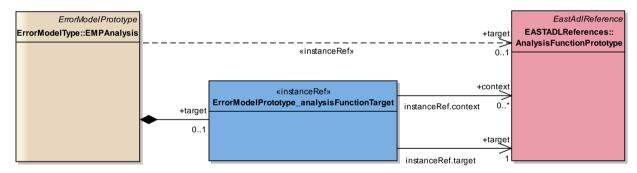

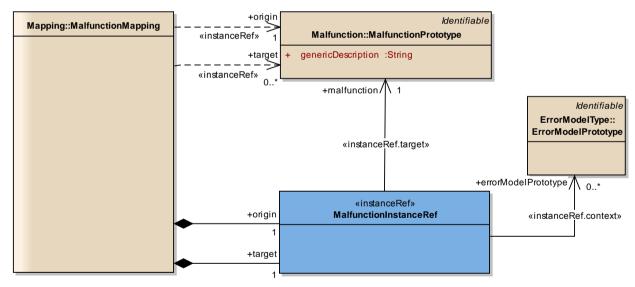

| Figure 39 : WT3.3.1 EMPAnalysis InstanceRef proposal                                            | 82 |

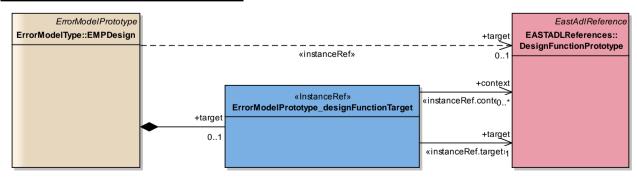

| Figure 40 : WT3.3.1 EMPDesign InstanceRef proposal                                                  | 82  |

|-----------------------------------------------------------------------------------------------------|-----|

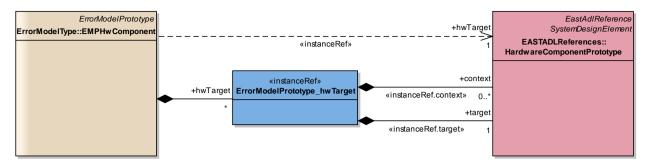

| Figure 41: WT3.3.1 EMPHwComponent InstanceRef proposal                                              | 83  |

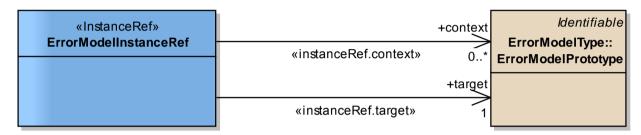

| Figure 42: WT3.3.1 ErrorModelInstance InstanceRef proposal                                          | 83  |

| Figure 43: WT3.3.1 ErrorModelMapping InstanceRef proposal                                           | 83  |

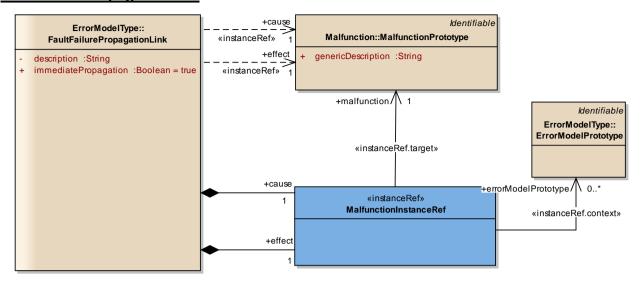

| Figure 44: WT3.3.1 FaultFailurePropagationLink InstanceRef proposal                                 | 84  |

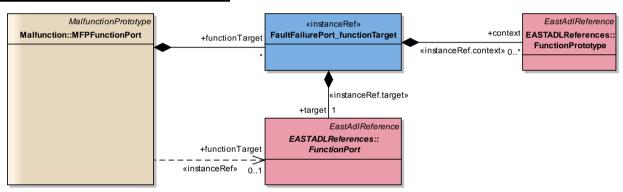

| Figure 45 : WT3.3.1 MFPFunctionPort InstanceRef proposal                                            | 84  |

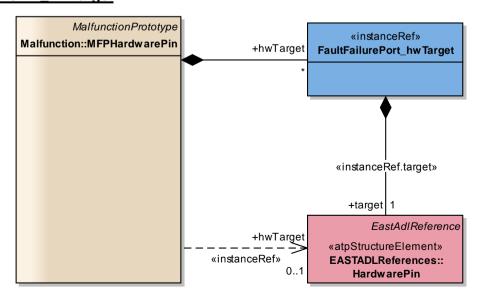

| Figure 46 : WT3.3.1 MFPHardwarePin InstanceRef proposal                                             | 84  |

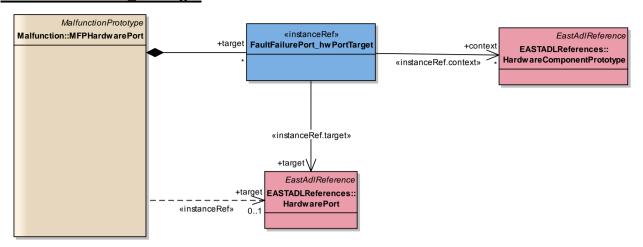

| Figure 47 : WT3.3.1 MFPHardwarePort InstanceRef proposal                                            | 85  |

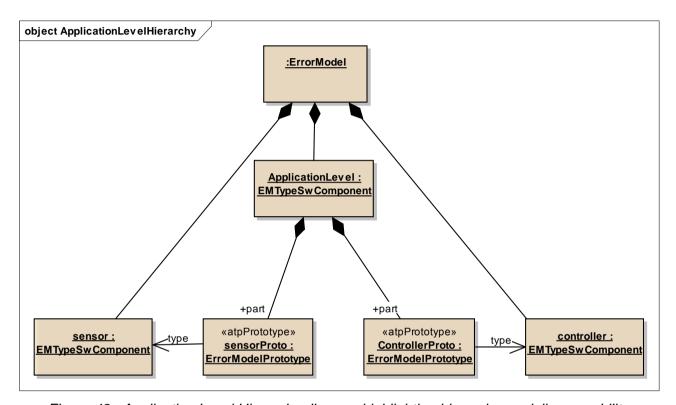

| Figure 48 : Application Level Hierarchy diagram highlighting hierarchy modeling capability          | 88  |

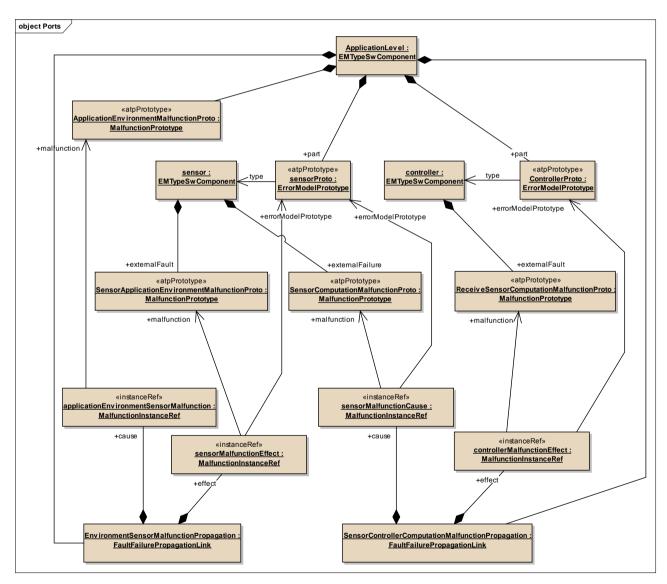

| Figure 49 : Application Level Hierarchy refinement with malfunctions added                          | 89  |

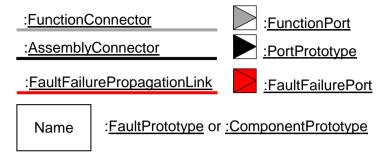

| Figure 50: Pattern legend for Applicability                                                         |     |

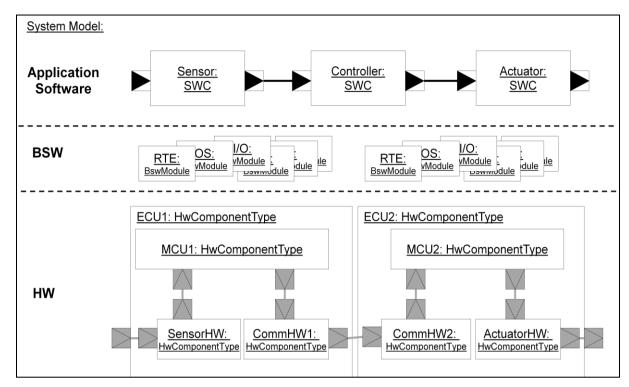

| Figure 51 : System model Representation                                                             | 91  |

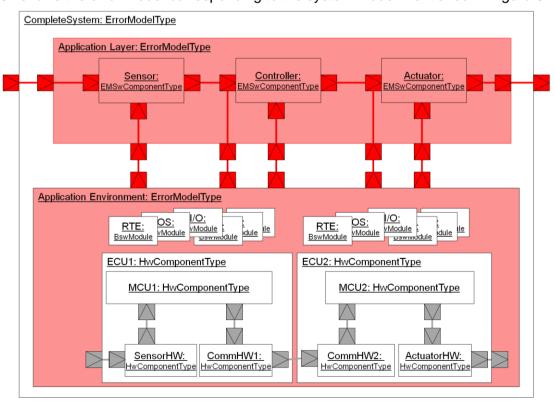

| Figure 52 : ErrorModel corresponding to Refined System model                                        | 93  |

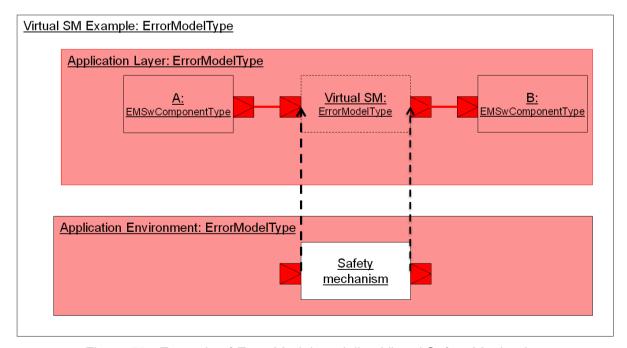

| Figure 53 : Example of Error Model modeling Virtual Safety Mechanism                                | 94  |

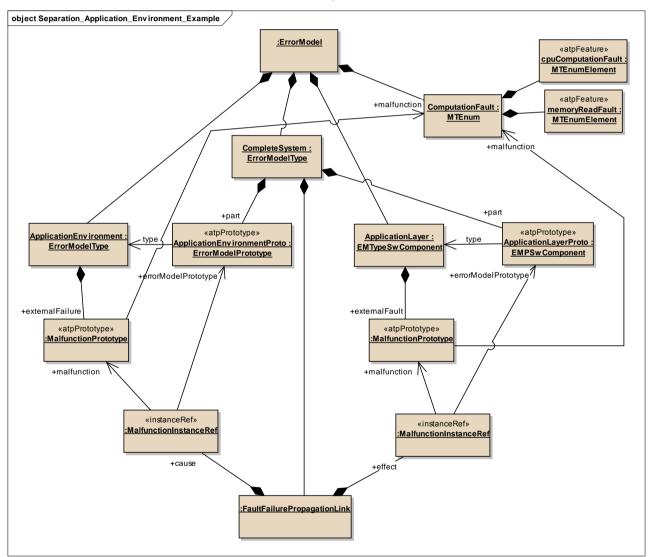

| Figure 54 : Example of modeling of the separation between the application layer and the environment |     |

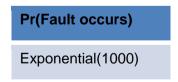

| Figure 55 : Fault dependencies of the motivating example                                            | 97  |

| Figure 56 : Fault dependencies of the previously described example                                  | 102 |

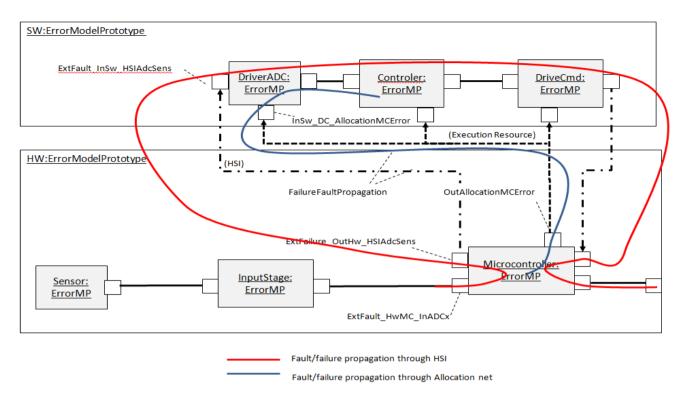

| Figure 57: Hardware – Software Fault propagation                                                    | 105 |

© 2013 The SAFE Consortium 7 (114)

# 3 List of tables

| Table 1 : Example of recognized analyzes methods listed by ISO26262 [1]                         | 14 |

|-------------------------------------------------------------------------------------------------|----|

| Table 2 : Synthesis table of assessment of most relevant safety analyzes methods using criteria | 15 |

| Table 3 : Type of safety analysis methods required or recommended by ISO26262 [1]               | 17 |

| Table 4 : Metrics allocation required or recommended by ISO26262 [1]                            | 20 |

| Table 5 : HiP-HOPS Valve example                                                                | 34 |

| Table 6 : Type of analysis methods required or recommended by ISO26262                          | 42 |

| Table 7 : Example of Valve Internal failure modes                                               | 43 |

| Table 8 : Mapping of AltaRica versus EAST-ADLV2.1 ErrorModel                                    | 48 |

| Table 9 : Pros and Cons table for HiP-HOPS and AltaRIca                                         | 50 |

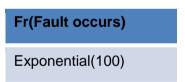

| Table 10 : Probability for CPU computation error                                                | 97 |

| Table 11 : Probability for memory corruption                                                    | 97 |

© 2013 The SAFE Consortium 8 (114)

#### 4 Executive Summary

The work task 3.3.1 targets to address the fault modeling and its propagation along the complete development lifecycle. This activity includes the definition of the necessary elements that are needed to capture fault information and propagation concept to produce safety analyses.

Existing fault modeling language candidates such as HiP-HOPS and AltaRica have been deeply analyzed to derive needs for the error modeling as proposed by WT3.3.1.

The starting point for error modeling is the existing modeling approach of EAST-ADLV2.1 tightly coupled with the system model by enriching existing architectural elements with its "fault behavior" in terms of an error model.

The Error model proposed by WT3.3.1 allows to represent the erroneous behavior of a system element as a black box view via the means of ErrorModelTypes (only external visible faults and failures are described) or as a white box view by allowing to a) decompose an ErrorModelType by an arbitrary number of ErrorModelPrototypes and "wiring" the visible malfunctions (faults, failures) between them and b) provide a language for atomic error models to relate internal faults and external faults to their external failures.

In a first step, the mechanisms of error modeling shall be the basis to conduct qualitative safety analyzes. In a second step they shall be extended to conduct quantitative safety analyzes in closed relation with work performed by WT3.2.2.

© 2013 The SAFE Consortium 9 (114)

#### 5 Scope of WT 3.3.1 and structure of the document

## 5.1 Scope of WT 3.3.1

Embedded in work package 3, work task 3.3.1 deals with failure and cutset analysis. The basis for this work task is the dependability part of EAST-ADLV2.1 which is presented in chapter 9.

WT3.3.1 aims to address the fault modeling and its propagation along the complete development lifecycle and a meta-model extension suitable for the following topics to WT4.2.3.

For the fault modeling language candidates, the needs, regarding fault information and propagation concept to be captured in the model to perform qualitative safety analyzes, will be identified. These artifacts are intended to be attached to each block of an architecture (fault models for inputs, outputs and block propagation), whatever level it is (functional, logical or physical organic or any mix of both). In addition, the same tools shall be used to compute the qualitative safety analyses for evaluation and consolidation of the functional and/or the technical safety concept. The fault and failure context for safety scenarios shall be extracted from safety requirement analysis and then captured using semantics of a fault modeling language. The safety concept will be validated thanks to propagation and analysis of these fault models. At implementation level on the hardware (HW) side, random hardware failure of hardware design and components (failure in time rates) will be considered. In particular, the failures relations to the upper safety concept and theirs contributions to the overall safety analysis will be encompassing. For the hardware architecture, the objective is to extend previous qualitative analyses and to perform quantitative safety analyses with the final goal to work out ISO26262 metrics, such as Single Point Fault Metric (SPFM), Latent Fault Metric (LFM) and Probabilistic Metric HW Failures.

At implementation level on the software (SW) side, failure mode and propagation from the fault modeling language will extend AUTOSAR templates. Relation to the upper safety concept and theirs contributions to analysis will be encompassing. Such failure information will be either captured manually or defined from a tool, as the feasibility study of extraction of Matlab Simulink behavioral model. Additionally, probability of occurrence of the software failure mode will be investigated according to hardware element

Such work will be fertilized by preliminary work performed in the ATESST2 and SPEEDS projects, but also from aeronautic experience regarding the use of Altarica language, with possible use of a subset of it. The final outcomes of this task are an extension of the relevant meta-model to support the failure semantic (this document), and a tool specification for the failure analysis (see D331b document).

#### 5.2 Structure of the document

In a first step, the ISO26262 concepts addressed by WT3.3.1 to evaluate risk of malfunctioning behavior will be explained, including the selection of most relevant safety analyses methods for D331b.

In a second step, the problematic of evaluating malfunctioning behavior in distributed developments mixing OEM, Tier 01 and Tier 02 will be highlighted, and a contract approach will be proposed.

In a third step, HiP-HOPS and AltaRica will be analyzed, and the orientation taken in WT3.3.1 will be justified with some requirements for a simplified SAFE language.

Finally, in a fourth step, the gap between EAST-ADLV2.1 meta-model and previous analysis steps will be documented and an extension of the meta-model will be proposed with application rules.

© 2013 The SAFE Consortium 10 (114)

## 6 ISO26262 concepts addressed by WT3.3.1 to evaluate risk of malfunctioning behavior

# 6.1 Short Overview of ISO26262 Chapters of interest for WT3.3.1

During the development of a safety critical E/E product, ISO26262 requires or recommends, depending on the criticality of the product to be developed, to perform a certain number of activities, dealing with risk assessment, that are encompassed in safety analyses. The goal of safety analyses is to help evaluating early during the development phase the potential risks of malfunctioning behavior and find adequate safety measure to eradicate or mitigate their effects. ISO26262 chapters, where the evaluation of potential risks using safety analyses is useful, are illustrated hereafter:

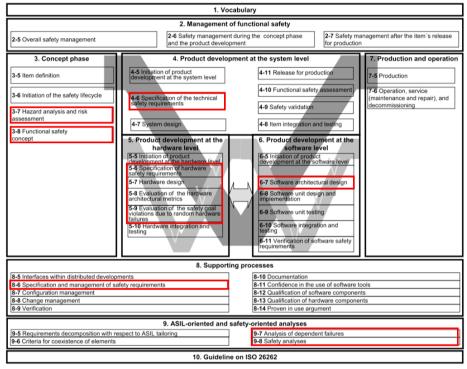

Figure 1: ISO26262 General Overview [1] highlighting where safety analyzes can help

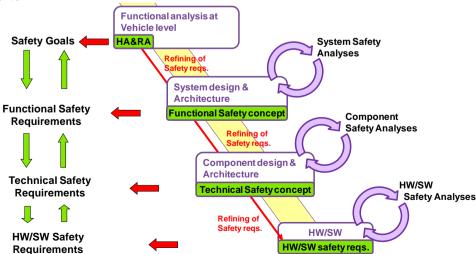

Safety analysis are used to support the concept and development design phase activities during which safety requirements, derived from safety goals, are refined up to HW/SW requirements as illustrated hereafter:

Figure 2: View of safety requirements refinement supported by safety analyses during the concept and development design phases

© 2013 The SAFE Consortium 11 (114)

# 6.2 ISO26262 and General concept of Fault / Error / Failure for malfunctioning behavior and its propagation

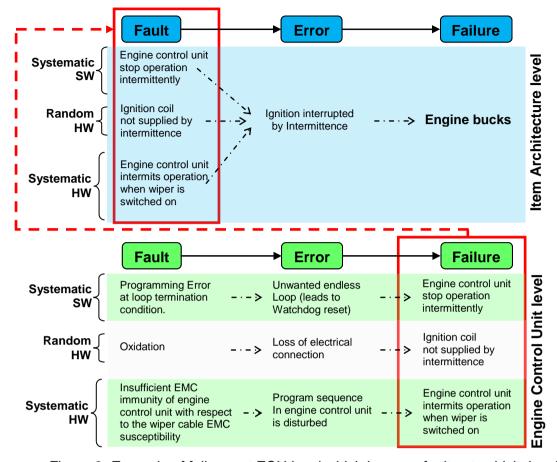

ISO26262 (see [1]) defines **fault** / **error** / **failure** concepts for **malfunctioning behavior**, their interaction and their propagation through different architecture hierarchy levels up to vehicle level:

- A fault is an abnormal condition that can cause an element or an item to fail.

- An error is defined as the deviation between a computed, observed or measured value or condition from theoretically correct value or condition.

- A **failure** is the termination of the ability of an element, to perform a function as required.

- A **malfunctioning behavior** is a failure or unintended behavior of an item with respect to its design intent.

Therefore an error can be caused by a fault (abnormal condition), and lead to a failure which can be a malfunctioning behavior if appearing at item level.

Faults and failures can be of different types: systematic or random.

- Systematic faults or failures are manifested in a deterministic way. They can only be eliminated by a change of the design or the manufacturing process and cannot be quantified.

- Random fault or failures only concern HW elements. They occur unpredictably during the lifetime due to physical causes and follow a probability distribution that allows us to predict Random HW failure rates.

SW faults and failures are always systematic. If you find a scenario that causes a failure, it leads each time to the same failure. In this case, only a design change can eliminate the systematic fault that causes the failure.

HW faults/failures can be either systematic or random.

- Systematic HW: If, as an example, an Electronic Control Unit (ECU) is not protected enough against EMC produced by an external neighbor cable from the system, it always leads to the same failure of the ECU. Only a design change to improve EMC protection would eliminate the systematic faults and failures.

- Random HW: if, as an example, an abnormal oxidation occurs randomly on an HW part belonging to an Electronic Control Unit (ECU), it might lead to a loss of electrical connection and therefore lead to a failure of the ECU.

<u>Note:</u> When systematic faults/failures and HW random faults/failures are mixed together in a same safety analysis such as a Fault Tree Analysis, so to be able to produce quantitative evaluation, it is needed to quantify systematic faults/failures to not produce erroneous probability calculations.

As an example, if a systematic fault/failure is contributing to an AND Gate in a Fault Tree Analysis, its probability of occurrence should be set to 1 to avoid erroneous probability calculation at AND Gate level.

As another example, if a systematic fault/failure is contributing to an OR Gate in a Fault Tree Analysis, its probability of occurrence should be set to 0 to avoid erroneous probability calculation at OR Gate level.

© 2013 The SAFE Consortium 12 (114)

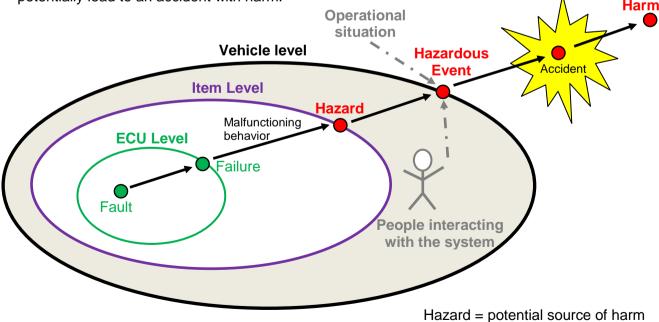

A failure at one architectural level (e.g. ECU level) can become a fault at an upper architectural level (e.g. item level) as shown hereafter.

Figure 3: Example of failures at ECU level which become faults at vehicle level

The fault can propagate in the system to produce an hazard at item level, which can become an hazardous event at vehicle level when combined with particular operational situation, and so potentially lead to an accident with harm.

Figure 4: Example of a fault propagating to a hazard

© 2013 The SAFE Consortium 13 (114)

## 6.3 Types of Safety Analyzes recommended by ISO26262

Through the different concept and development phases from the safety lifecycle, ISO26262 recommends or requires, depending on the criticality of the items or elements to be developed, to perform safety analyses.

The objective of safety analyses is to support the derivation of safety requirements from the safety goals, and to validate and verify their effectiveness and completeness.

Safety analyses help to identify the effect of faults and failures on the functions, behavior and design of items or elements. They also provide information on conditions and causes that could lead to the violation of a safety goal (top-level safety requirement) or a safety requirement. In such a case, additional actions or safety measures shall be determined to eradicate or mitigate the effect of faults and failures.

The fault and failures considered in safety analyses can be either random or systematic, and either internal or external to the items or elements to be developed.

Safety analyses are either inductive or deductive.

- Inductive analysis methods are bottom-up methods that start from known causes and forecast unknown effects. Inductive methods are required by ISO26262 for ASIL A to ASIL D safety goals.

- Deductive analysis methods are top-down methods that start from known effects and seek unknown causes. Deductive methods are required by ISO26262 for ASIL C and ASIL D safety goals and only recommended for ASIL B safety goals.

Safety analyses are qualitative or quantitative:

- Qualitative analyses can be first appropriate and sufficient in most cases to identify failures and when it is not needed to predict the frequency of failure e.g. systematic failures.

- Quantitative analyses extend qualitative safety analyses, in a second step, only

when random hardware failures must be predicted as well as the hardware

architectural metrics and the evaluation of safety goal violation due to random

hardware failures. Quantitative analyses are not required to be applied to

systematic failures e.g. software failures.

ISO26262 does not require a specific analysis method but list recognized methods as follows:

| Qualitative analysis methods include:                                                                                                                                                                                                              | Quantitative analysis methods include:                                                                                                                                                                                                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Qualitative FMEA<sup>1</sup> (inductive)</li> <li>Qualitative FTA<sup>2</sup> (deductive)</li> <li>HAZOP<sup>3(mixed between inductive and deductive)</sup></li> <li>Qualitative ETA<sup>4</sup> (inductive)</li> <li>Ishikawa</li> </ul> | <ul> <li>Quantitative FMEA<sup>1 (inductive)</sup></li> <li>Quantitative FTA<sup>2 (deductive)</sup></li> <li>Quantitative ETA<sup>4 (inductive)</sup></li> <li>Markov models<sup>(inductive)</sup></li> <li>Reliability Block Diagrams<sup>(deductive)</sup></li> </ul> |

| <sup>1</sup> FMEA: Failure Mode Effect Analysis <sup>2</sup> FTA: Fault Tree Analysis <sup>3</sup> HAZOP: HAZard and OPerability analysis <sup>4</sup> ETA: Event Tree Analysis                                                                    |                                                                                                                                                                                                                                                                          |

Table 1: Example of recognized analyzes methods listed by ISO26262 [1]

Additionally, the safety analyses might also contribute to the identification of new functional or non-functional hazards not previously considered during hazard analysis and risk assessment.

## 6.4 Considered safety analyzes in WT3.3.1 (D331b)

As explained in chapter 5.1, the scope of WT3.3.1 is a first step to define the concepts needed for fault/failure propagation, documented in the D331a deliverable. In a second step, it is to define a tool specification for most relevant safety analysis methods that will permit to visualize and analyze the results from the fault/failure propagation (D331b deliverable).

Nevertheless to be coherent with fault/failure propagation, it was decided to select the most relevant safety analysis methods during first step and give the results in D331a deliverable.

# 6.4.1 Criteria-based assessment of most relevant safety analyzes methods using criteria

The different methods were assessed using different criteria as shown in the table hereafter:

| YES, NO criterion when answer is sure                                                                                | Inductive methods                                          |                                                                          |                                                   | Deductive methods                     |                                                              |  |

|----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------|---------------------------------------|--------------------------------------------------------------|--|

| Maybe: theoretically possible but never seen Limited: when it is not fully capable                                   | FME(D)A                                                    | ETA                                                                      | Markov                                            | FTA                                   | RBD                                                          |  |

| Capability to address ISO26262 requirements concerning qualitative / quantitative safety analyzes.                   |                                                            |                                                                          |                                                   |                                       |                                                              |  |

| Does this method allow performing qualitative and quantitative analyzes?                                             | YES  Qualitative FMEA  Quantitative FMEDA                  | YES                                                                      | YES                                               | YES                                   | YES                                                          |  |

| Can this method be performed at different architectural levels?                                                      | YES                                                        | YES                                                                      | YES theoretically but very complex at low level   | YES                                   | YES                                                          |  |

| Can this method address systematic failure?                                                                          | YES<br>FMEA                                                | YES                                                                      | YES                                               | YES but<br>Low interest               | YES but<br>Low interest                                      |  |

| Can this method address random failure?                                                                              | YES                                                        | YES                                                                      | YES                                               | YES                                   | YES                                                          |  |

| Can this method be used to calculate architectural metrics (SPFM & LPFM)?                                            | YES<br>FMEDA                                               | Maybe<br>but not direct                                                  | Maybe but not direct                              | Maybe<br>but not direct               | Maybe<br>but not direct                                      |  |

| Can this method be used to estimate the residual risks of safety goal violation                                      | Yes Failure Class at part level or estimation from FMEDA   | Maybe but not direct                                                     | Maybe possible but not direct                     | YES<br>PMHF                           | Maybe<br>but not direct :PMHF                                |  |

| Does this method support analysis of dependent failure?                                                              | YES                                                        | YES                                                                      | YES                                               | YES                                   | YES                                                          |  |

| Automation capabilities                                                                                              |                                                            |                                                                          |                                                   |                                       |                                                              |  |

| Does this method allow mapping with architecture?                                                                    | NO                                                         | NO                                                                       | NO<br>State machine                               | Limited Possible but restrictions     | Limited (no direct<br>mapping when<br>representing failures) |  |

| Can local analyses be generated from models?                                                                         | YES                                                        | Maybe but not direct because of success?                                 | Maybe If state machine behavior defined in blocks | YES                                   | YES                                                          |  |

| Can this method be transformed into another method without loss of information?                                      | YES ETA but only for failure not success, FTA for cutset 1 | Limited (only<br>failure not success)<br>FMEA, FTA with<br>cutset 1 only | NO<br>Only input for other<br>methods             | YES<br>FMEA for cutset 1,<br>RBD      | YES<br>FMEA for cutset 1, FTA                                |  |

| Can global analysis be build from local analysis?                                                                    | YES                                                        | Maybe but not direct                                                     | NO<br>Make no cense                               | YES<br>Transfert gates                | YES                                                          |  |

| Can this method be coupled with another analysis?                                                                    | YES<br>FTA, RBD event                                      | YES<br>FTA, RBD, Markov                                                  | YES<br>FTA, RBD; ETA                              | YES<br>FMEA, ETA events               | YES<br>FMEA, ETA events                                      |  |

| Post-processing capabilities for results                                                                             | <b>3</b>                                                   |                                                                          |                                                   |                                       |                                                              |  |

| Can this method allow identifying Single Point Fault?                                                                | YES                                                        | YES                                                                      | YES                                               | YES                                   | YES                                                          |  |

| Can this method allow identifying Safety Mechanism covering a single point Fault?                                    | YES<br>FMEDA                                               | YES<br>Safety Mechanism is<br>a barrier                                  | YES<br>Safe state transition                      | YES<br>AND Gate                       | YES Adding of parallel element                               |  |

| Can this method allow identifying Latent Fault?                                                                      | YES<br>FMEDA                                               | Maybe but not direct                                                     | YES<br>Safety Mechanism<br>failure state          | YES<br>but not direct                 | YES<br>but not direct                                        |  |

| Does this method allow understanding and visualizing cut-sets?                                                       | YES<br>Only cutset 1                                       | YES<br>Only cutset 1                                                     | NO cutset computation                             | YES                                   | YES                                                          |  |

| Does this method allow understanding and visualizing failure sequence?                                               | YES                                                        | YES                                                                      | YES                                               | YES                                   | Maybe but not direct                                         |  |

| Can this method be configurable to analyze and display multiple failure analysis?                                    | NO                                                         | NO                                                                       | YES                                               | YES<br>Cutset analysis and<br>display | YES Cutset analysis and display                              |  |

| Does this method help indentifying path analysis, from Failure mode to end effect, and respective involved elements? | Limited For identification of involved elements            | Limited For identification of involved elements                          | Limited For identification of involved elements   | YES                                   | YES                                                          |  |

Table 2: Synthesis table of assessment of most relevant safety analyzes methods using criteria.

© 2013 The SAFE Consortium 15 (114)

The goal here was clearly not to fully describe all the safety analysis methods, because they are well known and already described in [2] and [3], but to investigate which are the most relevant for the tool specification D331b.

The considered analysis methods in D331b shall permit, first to answer most of ISO26262 requirements concerning qualitative and quantitative analyzes, then to allow semi-automation to help users to generate safety analyzes. It shall finally offer good post-processing capabilities to analyze results and identify weaknesses.

- HAZOP and Ishikawa technique are more qualitative methods for daily life and will not be considered in the tool specification D331b. They are very limited to address ISO26262 requirements concerning safety analyses and are not very compatible with tooling.

- Failure Mode and Effect Analysis (FMEA) is an example of inductive technique, as it starts from known causes and explore possible consequences. FMEA is a well known and accepted technique in the automotive industry. FMEA Analyses in ISO26262 are generally conducted in two steps:

- 1. Qualitative analysis during which failure modes and their effects are analyzed.

- 2. Quantitative analysis, when dealing with HW random faults, called FME(D)A (Failure Mode Effect and Diagnostic Analysis). FME(D)A permits to calculate the architectural metrics (Single Point Fault Metrics and Latent Fault Metrics) by introducing safety mechanisms with their diagnostic coverage (detection rate of the fault) stopping or mitigating the fault propagation as proposed in the ISO26262 Part 5 Annex E [1].

Therefore, even if full automation is maybe not reachable, FME(D)A is a serious candidate for the tool specification D331b.

• Event Tree Analysis (ETA) is a second example of inductive technique for identifying and evaluating the sequence of events in a potential accident scenario (failure and success) following the occurrence of an initiating event. This analysis technique is known in the automotive industry but not a current practice as compared with FMEA. It can be used potentially to study a specific event and to demonstrate and visualize the effectiveness of a safety mechanism (seen as barrier). It can permit to quantify results but would not permit to calculate the architectural metrics directly. Moreover the automation capabilities seem reduced.

Therefore the interest is limited and do not present additional value compared to FME(D)A. It is not a good candidate for the tool specification D331b.

Markov modeling is a third inductive technique suitable when the dynamic behavior of the system is needed to be studied. It can also be used to model complex interactions within the system when failure of a component can influence behavior of other components. In these two cases, traditional techniques such as FMEA, ETA, RBD or FTA are not relevant.

Nevertheless Markov analysis technique does not permit to address all qualitative and quantitative analyses required by ISO26262. It has limited automation capabilities and requires high skills for users for results post-processing. Other kinds of methods will be anyway needed and for all these reasons, and therefore it will not be addressed in the tool specification D331b.

• Fault Tree Analysis (FTA) is a deductive analysis technique that starts from known effects and explore possible causes (sometime described as "Top Down" approach). FTA is generally qualitative in a first step, and then quantified in a second step. FTA is composed of events and logical event connectors (OR-gates, AND-gates, etc...).

Possible results from the analysis are the listing and visualization of all combination of events (cutset) with their importance factor leading to the top event failure and the probability that this critical top event will occur during a specified time interval (when dealing with HW random faults).

FTA is a well known and accepted technique in the automotive industry. It can be used to address most of the ISO26262 requirements concerning safety analyzes, and can offer good post-treatment capabilities. Therefore, even if FTA generation seems difficult to be fully automated, FTA method is a serious candidate for the tool specification D331b.

Reliability Block Diagram (RBD) is another kind of deductive analysis technique known in automotive but not a current practice. RBD performs the system reliability and availability analyses on large and complex systems using block diagrams to show network relationships. The structure of the reliability block diagram defines the logical interaction of failures, within a system, that are required to sustain system operation (success oriented).

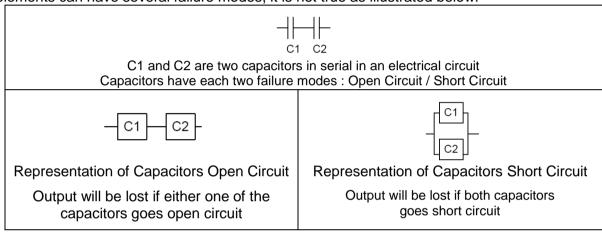

A lot of people have the preconceived idea that Reliability Block Diagrams always map with the physical arrangement of components in the system but it is not true. In certain cases when elements can have several failure modes, it is not true as illustrated below:

Figure 5: Example of RBD for 2 capacitors with several failure modes

To evaluate an RBD diagram there must be only one failure mode represented for each element. For elements with more than one failure mode, separate RBD diagrams must be drawn, one for each failure mode to avoid dependency problems. As in our systems, there is always more than one failure mode per element, the direct mapping between physical architecture and RBD will be unusual.

Therefore the interest in Reliability Block Diagram is limited and do not present additional value compared to Fault Tree Analysis. It is not a good candidate for the tool specification D331b.

## 6.4.2 Final choice for D331b

The ISO26262 (see [1]) required that inductive methods have to be used whatever the criticality (ASIL A to ASIL D) and deductive methods for ASIL C and ASIL D as shown in the table hereafter:

|                   | ASIL A                          | ASIL B      | ASIL C   | ASIL D   |

|-------------------|---------------------------------|-------------|----------|----------|

| Inductive methods | Required                        | Required    | Required | Required |

| Deductive methods | Nothing required or recommended | Recommended | Required | Required |

Table 3: Type of safety analysis methods required or recommended by ISO26262 [1]

Therefore for critical systems, we need to select at least one inductive method and one deductive method. Considering the results from chapter 6.4.1, for the tool specification D331b, as best comprise, the methods proposed will be derived from **FME(D)A** for inductive technique and **FTA** for deductive technique.

#### 7 Problematic of evaluating malfunctioning behavior in distributed developments

## 7.1 Illustration through an example

Fault propagation in complex integrated systems is a challenge. As illustrated in *Figure 3* and *Figure 4* from chapter 6.2, a lot of people think that when we analyzed a fault in a system, we always investigate if this fault can potentially violates a safety goal. In a simplified system such as described in ISO26262 Part 5 Annex E [1] made of a single ECU with sensors and actuators, this is possible, but in reality systems are often made of several ECUs, and therefore investigations are much more complex.

Moreover, most of the time, there is one system responsible (e.g. OEM), and the different ECUs are developed by different Tier 01 suppliers. Tier 01 suppliers themselves can buy SW or HW development from a Tier 02 supplier. It is a so called distributed development. In this context, the propagation of a fault in a HW element developed by a Tier 02 up to the violation of a safety goal is not so obvious.

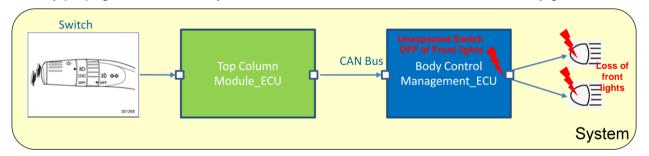

To illustrate the problematic of distributed development, let us take the example of a system whose desired function should consist in switching ON/OFF the front lights (low beams) of a car. If someone is driving by night in a dark area (operational situation) and the front lights are spuriously lost (malfunctioning behavior leading to hazard), it can be easily understood that this can lead to an hazardous event (ASIL B) for the driver, the other occupants of the car and potentially also people outside of the car. From the hazard analysis and risk assessment, safety goal corresponding to this hazardous event will be defined at our top level safety requirement. As this stage, the system is considered as a "black" box (we do not know how the desired function will be realized).

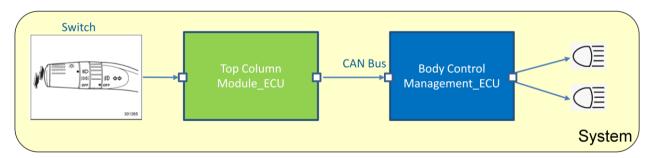

Then the system responsible will define first a functional architecture (not shown here) which will quickly lead to a preliminary architecture as shown hereafter that can realize the functional architecture. Of course, there is not only one unique technical solution to realize the functional architecture and therefore variants are possible.

Figure 6: Example of Preliminary Architecture of front lighting switch system

In this example, the driver can activate a switch (ring) on a lever and set ON/OFF the front lights (low beams). The corresponding electrical information is acquired by the Top Column Module ECU which then elaborates a Command that is sent on the CAN Bus. The Body Control Management ECU receives the Command from the CAN Bus and executes it.

© 2013 The SAFE Consortium 18 (114)

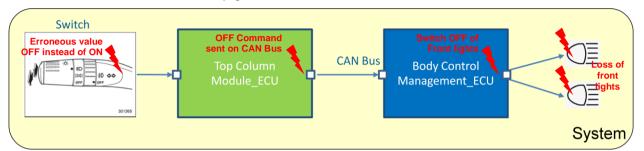

Based on a preliminary architecture as defined in *Figure 6*, the system responsible will have to identify, using relevant safety analyzes, the different malfunctions on the output of the components of its system that could propagate within the system and could violate the safety goal.

A malfunction of the output of the switch (e.g. erroneous value: OFF instead of ON) will be propagated to the Top Column Module ECU that will send an OFF value on the CAN Bus. Then the Body Control Management ECU will receive the erroneous value and will switch OFF the front lights. The initial switch malfunction will finally propagate without safety mechanism and lead to the violation of the safety goal.

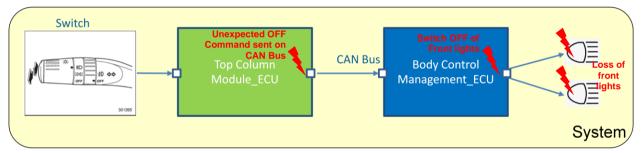

• In the same manner, a malfunction of the output of the Top Column Module ECU (e.g. unexpected OFF command sent on the CAN bus) will be received by the Body Control Management ECU that will switch OFF the front lights. The initial malfunction will finally propagate without safety mechanism and lead to the violation of the safety goal.

• In the same manner, a malfunction of the output of the Body Control Management ECU (e.g. unexpected OFF command execution) will switch OFF the front lights. The initial malfunction will finally propagate without safety mechanism and lead to the violation of the safety goal.

And also if both front light modules could have malfunction at the same time, it will lead to a loss

of front lights and will lead to the violation of the safety goal without safety mechanism.

In this simple example, a safety mechanism can be implemented in the Top Column Module ECU to detect a switch malfunction. It will be translated into one functional safety requirement: TCM-FSR\_001: TCM shall send a light parameter "Invalid" on the CAN bus in case of malfunction

And also to be sure that it does not lead to a loss of light, another functional safety requirement is needed for the Body Control Management ECU.

BCM\_FSR\_001 : When ignition switch is ON, BCM shall switch light ON if it receives a light parameter "Invalid" on the CAN bus : ASIL B

detection of lighting switch acquisition: ASIL B

That means that finally a loss of front lights in our system could mainly be due to a malfunction of the output of the Top Column Module ECU that could spuriously send an OFF command on the CAN Bus **OR** due to a malfunction of the output of the Body Management Control ECU that could spuriously switch OFF the front lights **OR** simultaneous malfunction of both Front lights.

As the criticality of the safety goal violated in this example is ASIL B, ISO26262 recommends only some metrics targets as shown in the Table hereafter:

|                           | ASIL A                          | ASIL B                 | ASIL C                 | ASIL D                 |

|---------------------------|---------------------------------|------------------------|------------------------|------------------------|

| Single Point Fault        | Nothing required or recommended | ≥ 90%                  | ≥ 97%                  | ≥ 99%                  |

| Metric (SPFM)             |                                 | Recommended            | Required               | Required               |

| Latent Fault Metric (LFM) | Nothing required or recommended | ≥ 60%<br>Recommended   | ≥ 80%<br>Recommended   | ≥ 90%<br>Required      |

| Residual risk             | Nothing required or recommended | < 10 <sup>-7</sup> / h | < 10 <sup>-7</sup> / h | < 10 <sup>-8</sup> / h |

| Metric                    |                                 | Recommended            | Required               | Required               |

Table 4: Metrics allocation required or recommended by ISO26262 [1]

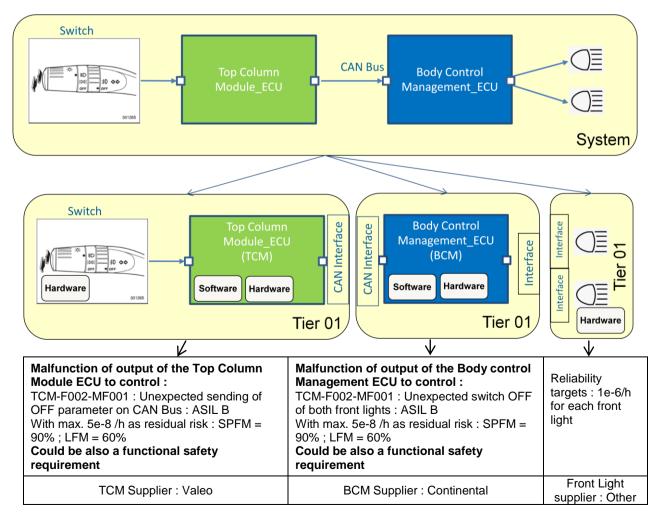

And if the system responsible (most of the time the OEM) decides to not perform the system development itself, but uses developments distributed to several suppliers (Tier 01). In this situation, it would be necessary to define the different interfaces between elements of the systems, as well as the critical malfunctions with associated allocated metrics.

Figure 7: Example of requirements allocation from OEM to suppliers in a distributed development

© 2013 The SAFE Consortium 20 (114)

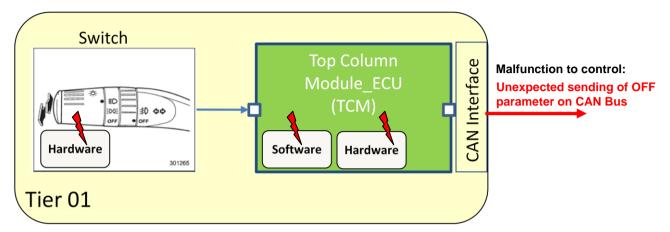

Therefore, when as in the example, the Top Column Module ECU supplier receives the working specification from the OEM, it will have to implement safety mechanisms in its product. These safety mechanisms shall stop or mitigate the propagation of SW and HW faults/failures leading to specified malfunctions outside of its component perimeter as shown hereafter:

Figure 8: Example of component perimeter known by a Tier 01 in distributed development

And at this level, it is never investigated at supplier level if it can lead or not to the violation of a safety goal. Indeed the system behavior is under the OEM responsibility and is not fully known by the supplier (Tier 01).

Of course, when safety analyses are performed inside the component to be developed and when new malfunctions propagating outside are discovered, the system responsible shall be immediately informed in order to analyze the impact at higher level.

To manage such scenario, a generic contract-based approach is proposed in chapter 7.2 in order to improve the formalism of expected behavior in distributed developments.

## 7.2 Contracts Approach in distributed developments

Contract-based design is a methodology that allows compositional reasoning. The methodology can be applied for different viewpoints like functional and/or dysfunctional behavior. It allows formal specification and analysis of component characteristics for safety-related systems. Component specifications given by contracts explicitly distinguish between promised behavioral characteristics which are guaranteed as long as behavior assumed for the component context hold. Assumptions and promises of contracts can be formally described e.g. by using a pattern-based specification language. These patterns allow the specification of safety-requirements which guarantee safety-concepts for components under the assumption that specific combinations of defined failures do not occur or are mitigated by safety mechanisms. Combination of contracts can be analyzed for a set of sub-components in a virtual integration test on implying contracts of a parent component composed by these sub-components.

## 7.2.1 Contracts Historical background

Many of the concepts for contract-based component design are results of the SPEEDS project (Speculative and Exploratory Design in Systems Engineering, EU, 6th Framework) [4], and draw on classic research on compositionality as well as more recent ones. Further activities regarding contract-based requirements engineering using a formal pattern-based requirements specification language (RSL) were performed within the project CESAR (Cost-Efficient methods and processes for SAfety Relevant embedded systems, ARTEMIS JU) [5].

© 2013 The SAFE Consortium 21 (114)

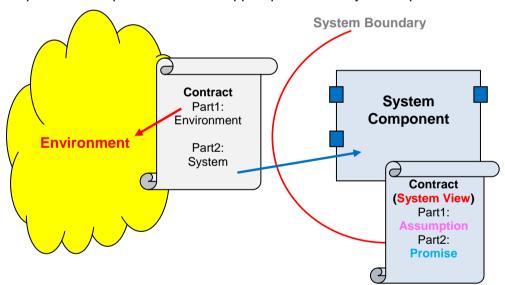

#### 7.2.2 Contracts basic description

Contract based modeling was developed in order to meet the requirements of cooperative systems. The idea is simple. A system is described by a set of components as depicted in Figure 9. A component can be decomposed into sub-components as parts of that component. Each component responsible part svstem element that to provide a number of well-defined services. However, in order to do so they need to rely on the properties of other interfacing components (i.e. they have assumptions on the behavior of the environment in which they are embedded). In turn they provide guarantees to other partners about their own behavior. Contract based specification methods address these issues by distinguishing what a component relies on and what it delivers. This kind of specification is especially useful when no actual implementation exits, for example during early development phases when only requirements and their relations are known, and can be used to establish the preliminary architecture. Due to the defined relationships between context components and sub-components as well as those among sub-components it is possible to evaluate the impact of the overall architecture layout on the different system requirements.

Having a complete and well-defined description of the interface of a component enhances the development of large systems. The definition of such well defined interfaces is a means that improves scalability, compositionality and abstraction. Re-use of components and design patterns, developing libraries of design components and better support for using COTS (Components Off The Shelf) are use-cases that benefit from this approach. Existing designs can be easily changed in order to adapt for new requirements or to support product family development.

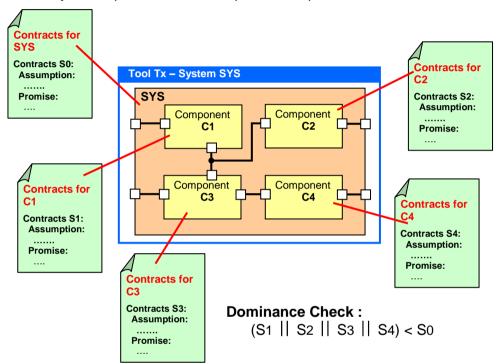

Figure 9: SPEEDS Contract based specification of interface properties [4]

Furthermore contract based modeling provides the necessary infrastructure for efficient compositional analyses, thus avoiding many of the complexity problems otherwise associated with large models. Evaluating the impact of different design choices and alternative implementations of a component helps in avoiding unnecessary cycles in the design process. Compatibility of components can already be tested during the early design phases.

Contract based modeling can be started early in the design process and supports an incremental design evolution with gradual improvements going from abstract models towards more and more refined ones. It enables the specification of well defined interface between components so that:

- each component (possibly collections of components) is associated with a contract that specifies the interface the component uses to interact with the environment

- contracts consists of a number of assumption-promise pairs

- the implementation of each component can be verified on its own, formal verification techniques can be used to validate that the component fulfils its contract

- compositional analysis of system-level properties can be based entirely on the contracts

of the individual components, so that issues of complexity and heterogeneity that arise

from detailed implementation can be avoided

- functional aspects of the system as well as non-functional properties, such as safety and reliability, can be addressed.

In the SPEEDS methodology [4] a virtual integration test composes the contracts and then verifies whether this assembly is consistent with the contracts of their parent component. This is the fundamental building block underlying the compositional analysis that ensure that the decomposition step was correct, in the sense that the defined sub-components will work together and satisfy the requirements of their parent component.

Figure 10: Virtual Integration of Heterogeneous Rich Components (HRC) [4]

Based on contracts, in particular two kinds of analyses are part of the virtual integration:

- **Compatibility Analysis:** This analysis verifies whether the assumptions and promises of interconnected respectively neighboring components are compatible with each other.

- Entailment Analysis: This kind of analysis, also known as dominance check, composes the contracts of a set of interconnected components and then verifies whether this assembly is consistent with the contracts of their parent component.

In the case of entailment, one can say that the contracts of the sub-components imply the contracts of their parent component. Both analyses together enable the developer to ensure that the decomposition step was correct, in the sense that the defined sub-components will work together and satisfy the requirements of their parent component, provided that the sub-components satisfy their own contracts. After the incremental verification and validation step, all derived sub-components are sufficiently characterized and can be designed independently. The developer now has the alternatives to iterate the decomposition step again, implement the sub-components or select an existing implementation from a library. The developer must ensure that any implementation that is provided, either newly developed or selected from a library, satisfies the sub-component's contracts.

#### 7.2.3 Contracts basic elements

The following chapter will give an overview of the basic elements considered by contract-based component design. Contracts are specifications for components with promised characteristics for an assumed environment of that component. Such specifications address characteristics which are observable at the interface of a component.

#### Contract

A contract is a requirement which is structured in two parts, a promise, which must hold provided that assumed characteristics of the component's environment are fulfilled, the assumption. Such a contract-based specification therefore distinguishes between assumptions on the usage context of a component and promised characteristics for the specified usage context. This is the basic principle of contract-based design approach in the SPEEDS project and of the HRC meta-model specification [6]. Contracts have two kinds of assertions, namely **assumption** and **promises**. These assertions can be described informally or in a formal way e.g. by using a pattern-based requirement specification language (RSL).

#### **Promise**

The promise describes guaranteed functional and non-functional characteristics in a contract-based specification. The promise of a contract, assigned to a component, has to hold provided that the assumptions are satisfied. If an assumption is not fulfilled then the promise does not necessarily hold.

#### **Assumption**

An assumption describes the assumed design environment for a contract-based specification. Assumptions characterize the allowed usage context for a component as well as specific use cases within the allowed usage. If a component is used accordingly to its assumptions, it will guarantee the behavior specified by the promise.

## Component

A contract is used to specify characteristics of a system, a sub-system or an element with defined interfaces, which is called a component. These component can be of various nature, like logical components that do not distinguish between hardware and software (typical used for functional safety concepts) or technical components (used to describe the technical safety concept). A component defines a set of interfaces which are addressed by the contracts assigned to the component. If a component is considered as a black-box then only its interfaces and its contracts are known. Otherwise a component can be decomposed into a composition of sub-components. Each sub-component can have its own contracts. In a clean architecture design the combination of contracts assigned to the sub-components implies the contracts of the parent component.

# 7.2.4 Contracts Failure Description

Pattern-based Safety Contracts are a means to define fault containment properties for a system's safety concept. The patterns describe how failures are contained and evaluate the impact on the top-level safety requirements. Containment is meant in terms of failure propagation. Failures can be contained (under given assumptions, defined in the contract) in a part of the system and does not further propagate. This kind of analysis can be done very early in the design process using abstract representation of the component and will be used to derive additional safety requirements. With the pattern presented in this chapter it is possible to create a specification of the containment or propagation of faults.

The main concepts used for this pattern are faults and failures and a combination of them in an expression. The pattern can be used to describe the combinations of faults in an assumption and combinations of failures or malfunctions in a promise of a safety-contract. As long as the specified assumption holds the non-occurrence of the specified failure is guaranteed for the system. Yet, if

© 2013 The SAFE Consortium 24 (114)

the assumption of the contract is violated, i.e. a combination of faults occurs, which is not expected, than the promise cannot be guaranteed anymore and the failure may occur anyway.

The following attributes are used in the pattern:

- Failure-Condition

- Degradation modes

- A mode expression consists of a mode variable, a mode name and a relational operator("= =", "!=")

- Example: DM==normal, DM != detected

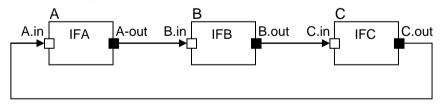

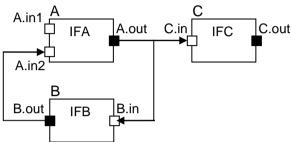

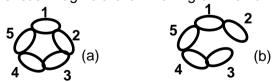

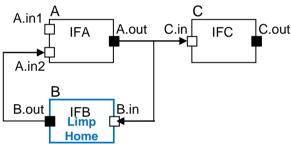

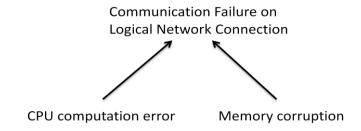

- Expression, Expression Sets