(ITEA 3 - 17003)

# PANORAMA Boosting Design Efficiency for Heterogeneous<sup>3</sup> Systems

#### **Deliverable:**

**Living Roadmap**

#### Work Package:

Contribution to ITEA Living Roadmap

#### Task:

State of the art

Data Models, Data transformation, Analysis Methods, Visualizations and

Data Traceability

DocumentType:DeliverableClassification:PublicDocumentVersion:Revision 1Contract Start Date:2019-04-01DocumentPreparation Date:2020-07-13Duration:2022-03-31

# History

| Rev. | Content         | Resp. Partner    | Date       |

|------|-----------------|------------------|------------|

| 1    | Initial version | Project partners | 2020-07-17 |

|      |                 |                  |            |

|      |                 |                  |            |

## **Contents**

| Hi | •    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ii   |

|----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Su |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ix   |

| 1  | Exe  | cutive Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1    |

|    | 1.1  | Purpose and objectives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1    |

| 2  | Proj | ect overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3    |

|    | 2.1  | Rationale of the project                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3    |

|    |      | 2.1.1 Problem statement and market value chain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3    |

|    |      | 2.1.2 Project innovations and technology value chain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6    |

| 3  | Stat | e of the art standards and data models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10   |

|    | 3.1  | AMALTHEA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

|    | 3.2  | AUTOSAR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 13 |

|    | 3.3  | SysML                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

|    | 3.4  | EAST-ADL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

|    | 3.5  | Rubus Component Model (RCM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

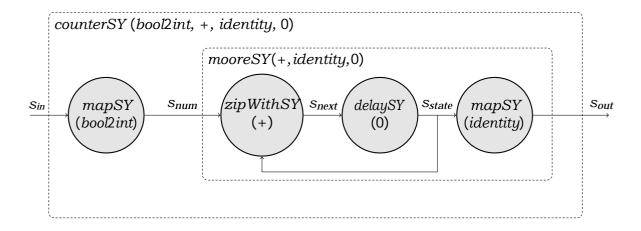

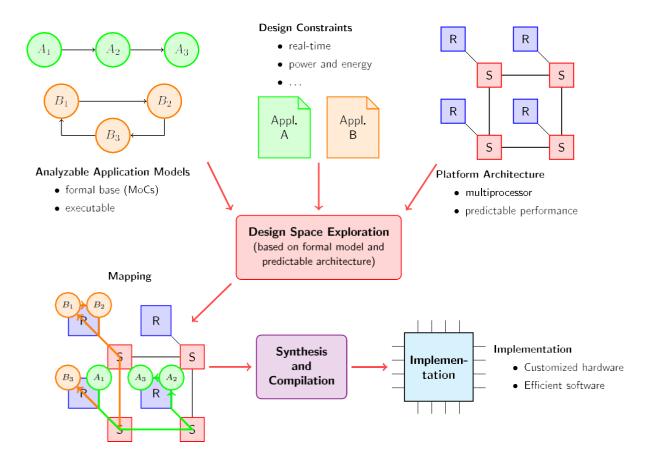

|    | 3.6  | ForSyDe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

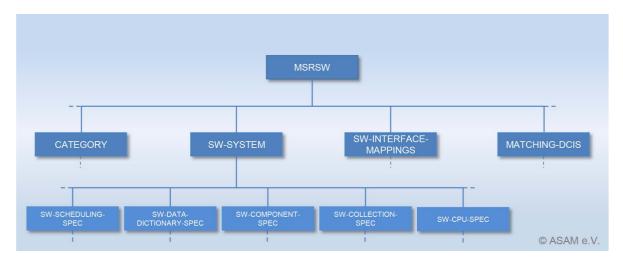

|    | 3.7  | ASAM MDX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

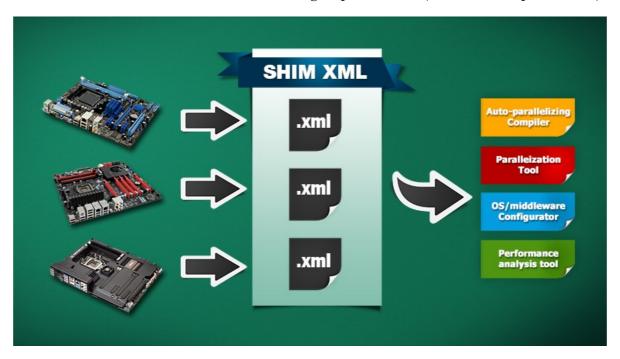

|    | 3.8  | SHIM 2.x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

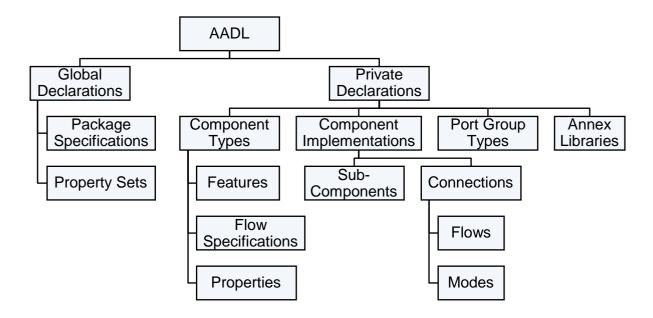

|    | 3.9  | AADL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

|    | 3.10 | Safety models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

|    |      | 3.10.1 EAST-ADL Error Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

|    |      | 3.10.2 AADL Error Model Annex (AADL EA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

|    |      | 3.10.3 SysML Failure Logic Extension                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

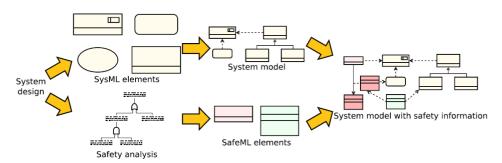

|    |      | 3.10.4 SafeML                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

|    |      | 3.10.5 Common Assurance & Certification Metamodel (CACM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

|    | 2 11 | 3.10.6 Open Dependability Exchange Meta-model (ODE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

|    | 3.11 | Event traces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

|    |      | 3.11.1 Detter/ Dest Trace Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

|    |      | 3.11.2 SQL database                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 34 |

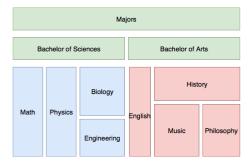

| 4  |      | traction Levels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 35   |

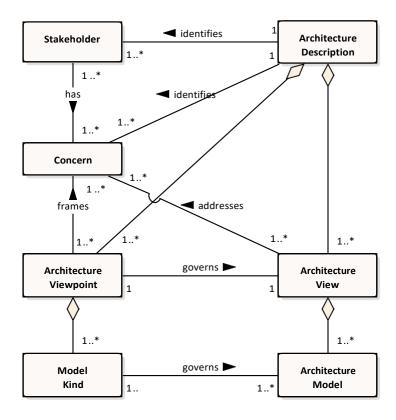

|    |      | ISO/IEC/IEEE 42010-2011                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

|    | 4.2  | Abstraction Levels in other Projects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

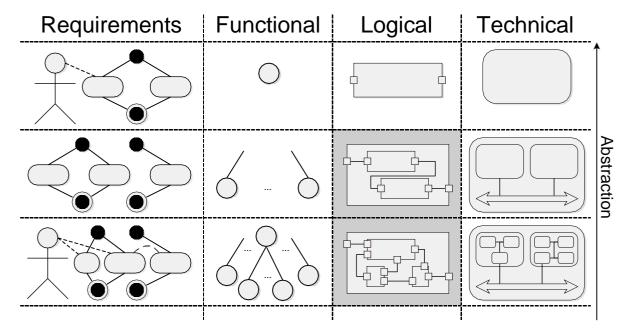

|    |      | 4.2.1 SPES2020 and SPES_XT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

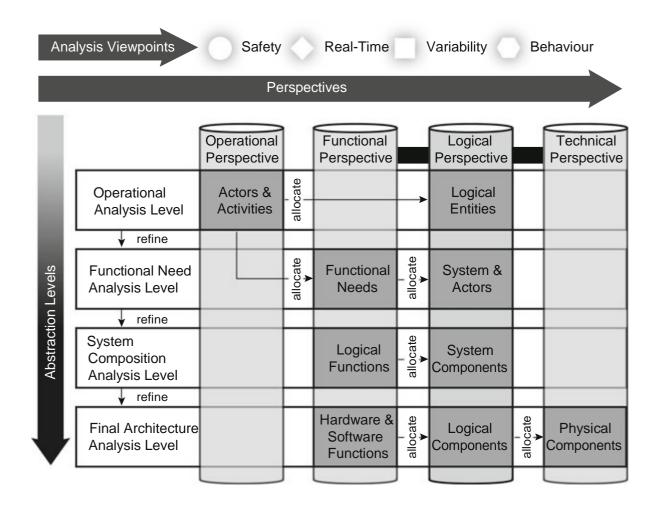

|    |      | 4.2.2 CESAR and CRYSTAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 38   |

| 5  | Stat | ic Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 40   |

| _  |      | and the second s |      |

## **Contents**

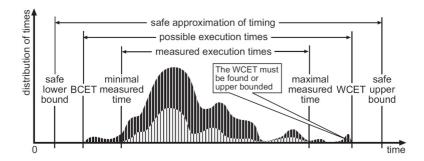

|   | 5.1  | Static Timing Analysis                                      | 40  |

|---|------|-------------------------------------------------------------|-----|

|   |      | 5.1.1 Memory Management                                     | 41  |

|   | 5.2  | Schedulability Analysis                                     | 42  |

|   |      | 5.2.1 Event chain analysis                                  | 43  |

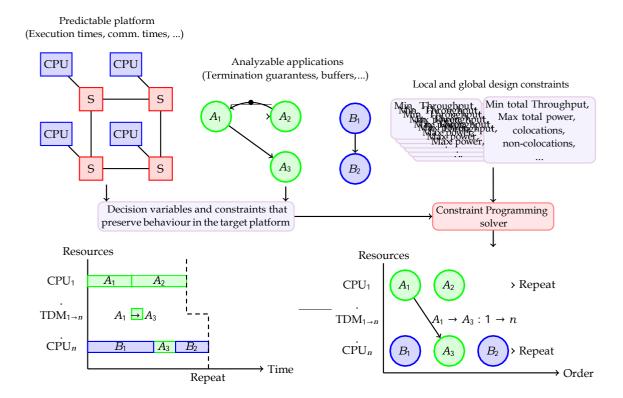

|   | 5.3  | Mapping and scheduling of Synchronous Dataflow Applications | 43  |

|   | 5.4  | Energy Analysis and Minimization                            |     |

|   |      | 5.4.1 Switching Capacitance per Processor Cycle             | 45  |

|   |      | 5.4.2 Adaptated ILP Formulation                             |     |

|   | 5.5  | Spatial Segregation Analysis for Software Deployment        |     |

|   |      | 5.5.1 Methodical Background                                 | 47  |

|   |      | 5.5.2 Analysis Prototype                                    |     |

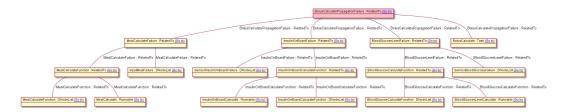

|   | 5.6  | Failure Propagation Analysis                                |     |

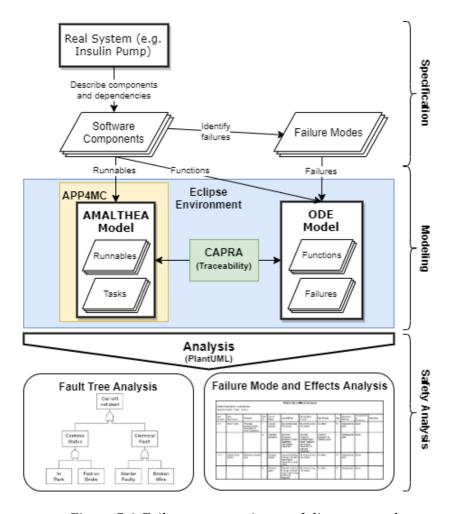

|   |      | 5.6.1 Approach                                              |     |

|   | 5.7  | Component Fault Tree (CFT) Methodology                      |     |

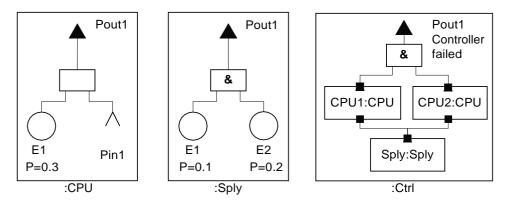

|   |      | 5.7.1 Overview                                              |     |

|   |      | 5.7.2 Example                                               |     |

|   |      | 5.7.3 Input                                                 |     |

|   |      | 5.7.4 Output                                                |     |

|   |      | 5.7.5 Advantages of the Component Fault Tree Methodology    | .56 |

| 6 | Dyn  | amic Analysis                                               | 57  |

|   | 6.1  | SystemC Simulation                                          | 57  |

|   |      | 6.1.1 Application of SystemC                                |     |

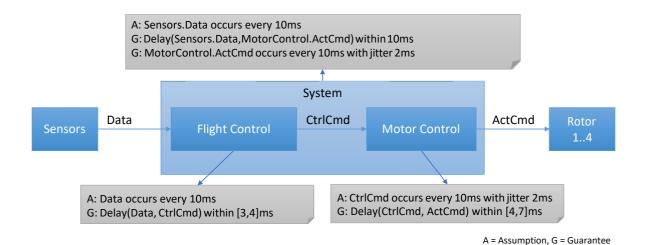

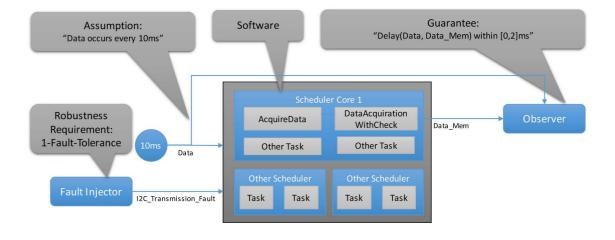

|   | 6.2  | Integration Testing for Timing Requirements                 |     |

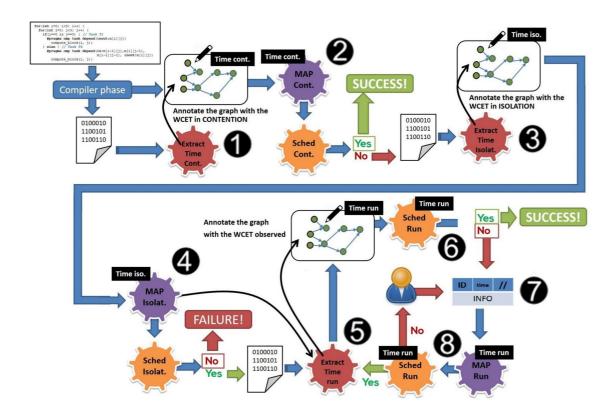

|   |      | 6.2.1 Methodical Background                                 |     |

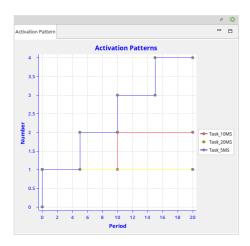

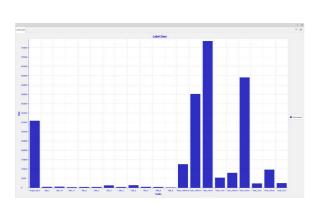

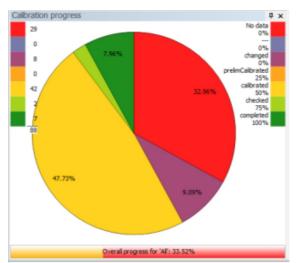

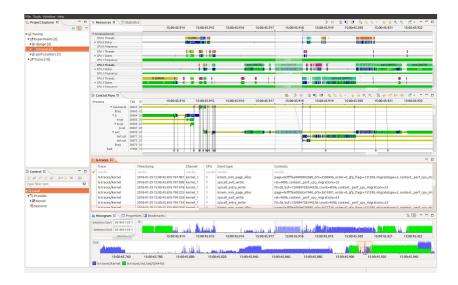

|   |      | 6.2.2 RTAna2                                                |     |

|   |      | 6.2.3 MULTIC Tooling                                        | 62  |

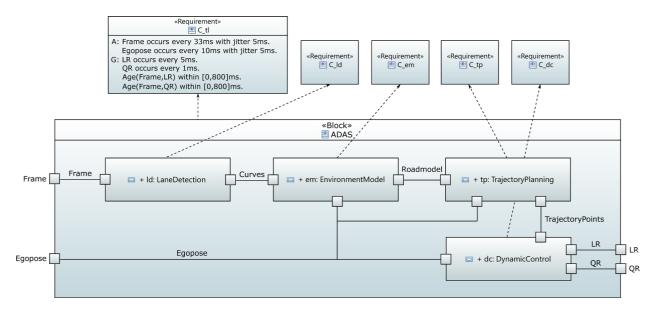

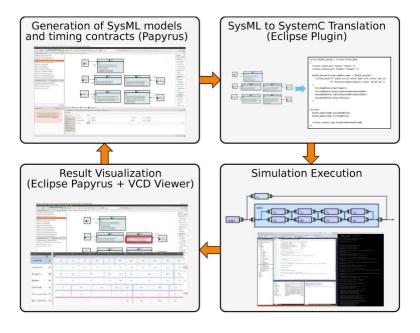

|   | 6.3  | Timing Simulation and Evaluation                            | 63  |

|   |      | 6.3.1 Development Process                                   | 65  |

|   |      | 6.3.2 Input                                                 | 65  |

|   |      | 6.3.3 Output                                                | 65  |

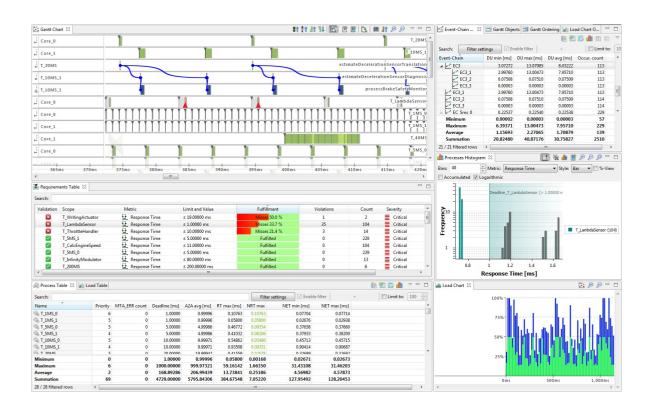

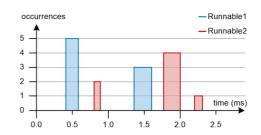

|   | 6.4  | chronSIM                                                    | 67  |

|   |      | 6.4.1 Simulation                                            | 67  |

|   |      | 6.4.2 Optimization                                          |     |

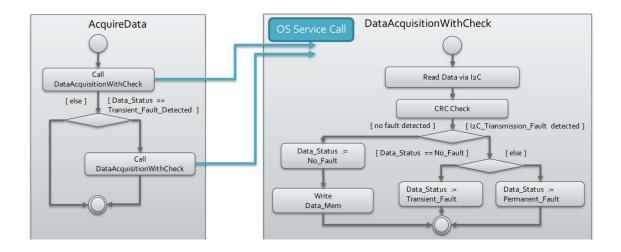

|   | 6.5  | Fault Propagation Analysis for Hardware                     | 69  |

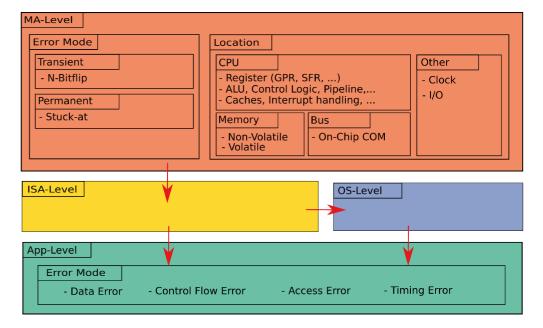

|   |      | 6.5.1 Fault Model                                           |     |

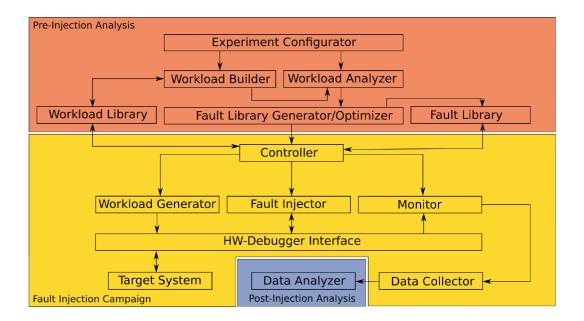

|   |      | 6.5.2 PyFI - Workflow and Design                            | 71  |

|   | 6.6  | Measurement-Based Timing Analysis                           | 73  |

| 7 | Visu | alization Techniques                                        | 76  |

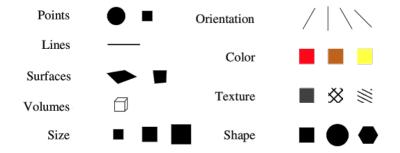

|   | 7.1  | Data Visualization                                          | 76  |

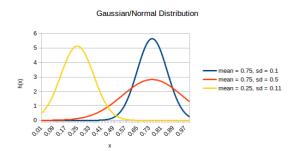

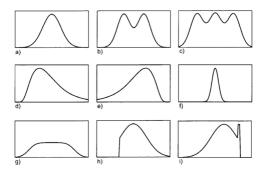

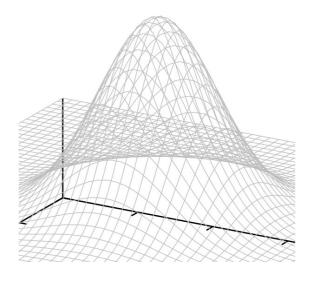

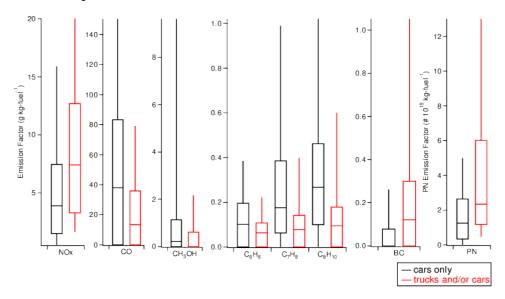

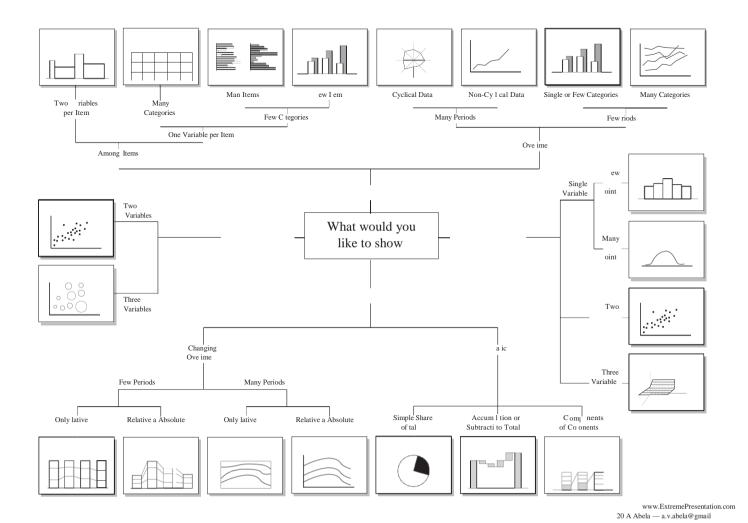

|   |      | 7.1.1 Charts                                                |     |

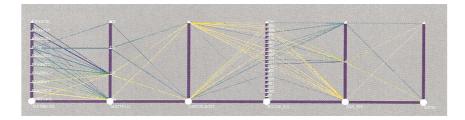

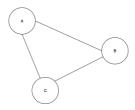

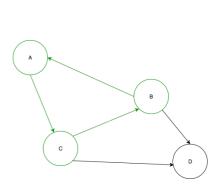

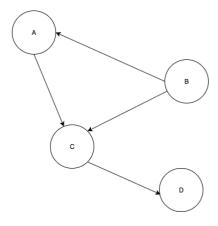

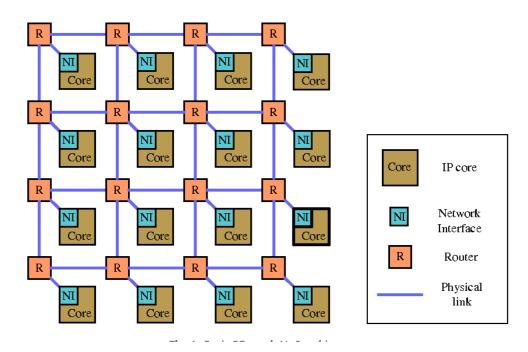

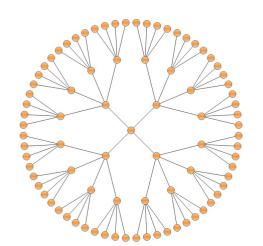

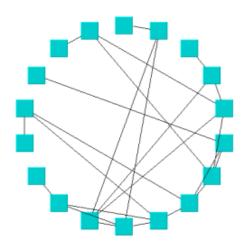

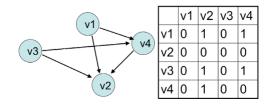

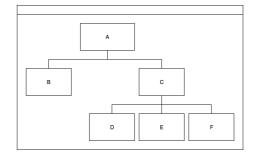

|   |      | 7.1.2 Graphs                                                | 81  |

|   |      | 7.1.3 Tools for Assessment                                  |     |

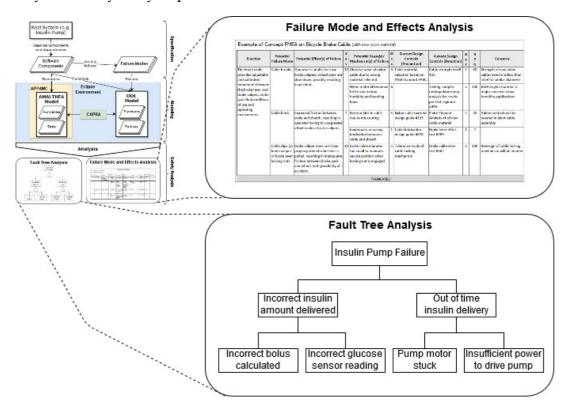

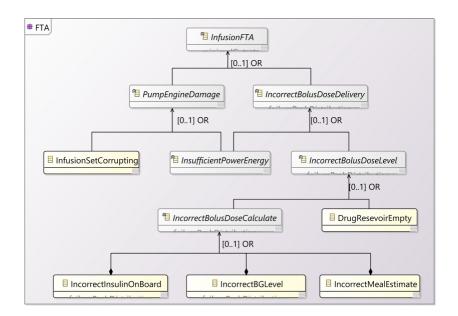

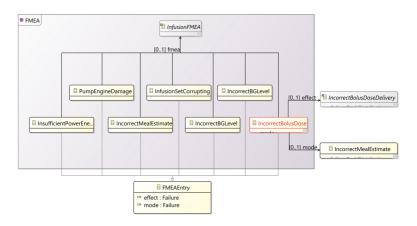

|   | 7.2  | Failure Propagation Visualization                           |     |

|   |      | 7.2.1 Safety Modelling Process                              |     |

|   |      |                                                             |     |

|   |      | 7.2.2 Conclusion                                            | 90  |

# **Contents**

| 8 | Stat | e-of-th | e-Art of Collaborative Development Processes          | 91 |

|---|------|---------|-------------------------------------------------------|----|

|   | 8.1  | Softw   | are Development Standard Process                      | 91 |

|   |      | 8.1.1   | PANORAMA Context                                      | 92 |

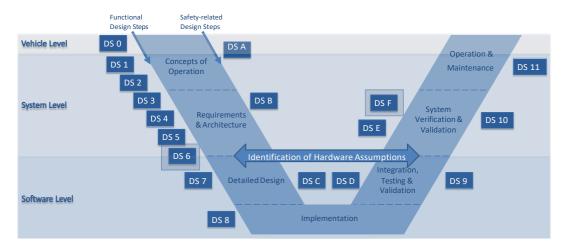

|   | 8.2  | Safety  | v-critical Systems Development Process                | 92 |

|   | 8.3  |         | borative Work in Tool Platforms                       |    |

|   |      | 8.3.1   | Document-centric Collaboration                        | 94 |

|   |      | 8.3.2   | Artifact-centric Collaboration                        | 94 |

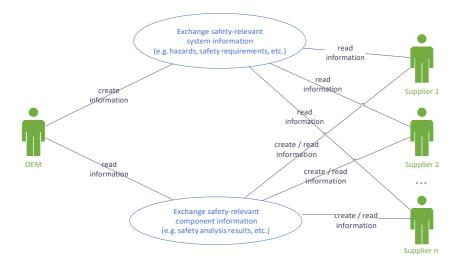

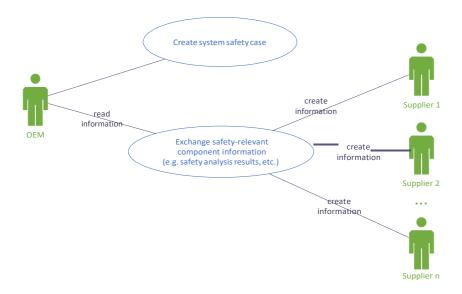

|   | 8.4  | Distri  | buted Dependable Systems Development                  | 95 |

|   |      | 8.4.1   | Collaboration Scenario: Requirement-driven Design     | 95 |

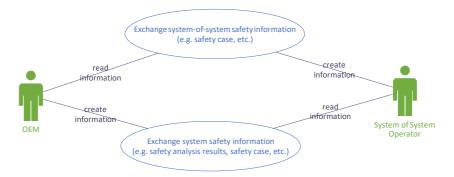

|   |      | 8.4.2   | Collaboration Scenario: Components-of-the-Shelf       | 96 |

|   |      | 8.4.3   | Collaboration Scenario: System-of-systems Integration | 96 |

|   |      | 8.4.4   | Challenges                                            | 96 |

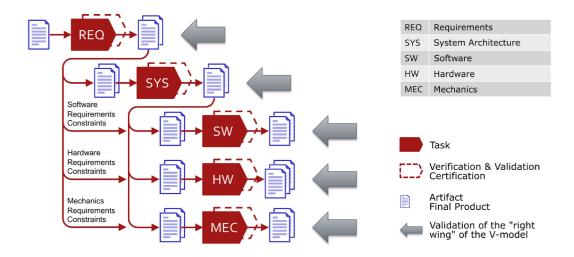

|   | 8.5  | ARAN    | MiS II Generic Process                                | 97 |

|   |      | 8.5.1   | User and System Requirements Engineering              | 97 |

|   |      | 8.5.2   | System Architecture                                   |    |

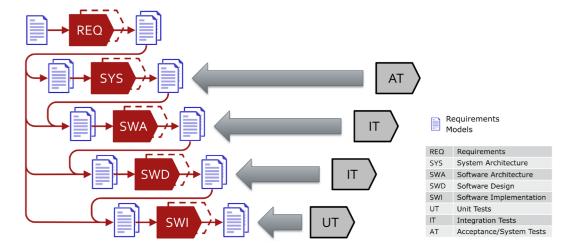

|   |      | 8.5.3   | Software Development                                  |    |

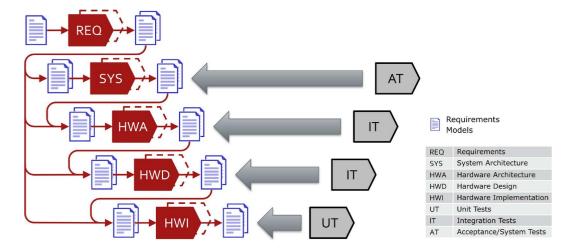

|   |      | 8.5.4   | Hardware Development                                  |    |

|   |      | 8.5.5   | Mechanics Development                                 | 98 |

|   |      | 8.5.6   | Verification and Validation                           | 98 |

|   |      | 8.5.7   | Importance for PANORAMA                               | 98 |

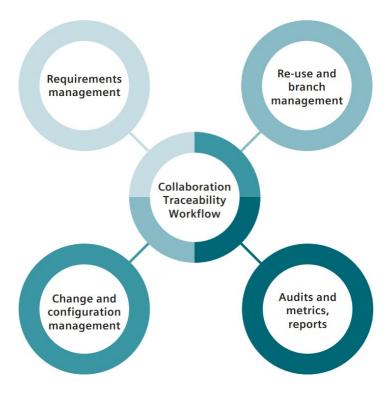

|   | 8.6  | Collal  | boration Traceability Workflow                        | 99 |

|   |      |         |                                                       |    |

# **List of Figures**

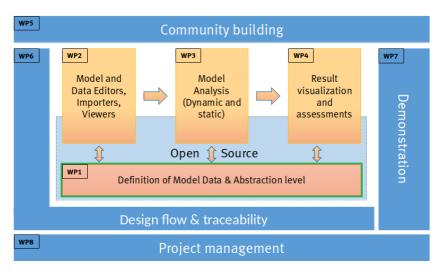

| 1    | PANORAMA Work Package Structure                                                            | ix |

|------|--------------------------------------------------------------------------------------------|----|