# ITEA 2 - 09033

# **TIMMO-2-USE**

Timing Model - Tools, algorithms, languages, methodology, USE cases

Report type Deliverable D13

Report name Methodology description V2

Report status Public

Version number Version 1.0

Date of preparation 2012-07-31

## **TIMMO-2-USE Partners**

AbsInt Angewandte Informatik GmbH

Arcticus Systems AB

Chalmers University of Technology

Continental Automotive GmbH

Delphi France SAS

dSpace GmbH

INCHRON GmbH

Institute National de Recherche en Informatique et Automatique INRIA

Mälardalen University

Rapita Systems Ltd, UK

RealTime-at-Work

Robert Bosch GmbH

Symtavision GmbH

Technische Universität Braunschweig

University of Paderborn

Volvo Technology AB

### **Project Coordinator**

Dr. Daniel Karlsson

Volvo Technology AB

Dept 6270, M2.7

405 08 Göteborg

Sweden

Tel.: +46 31 322 9949

Email: <a href="mailto:Daniel.B.Karlsson@volvo.com">Daniel.B.Karlsson@volvo.com</a>

## **Authors**

Cecilia Ekelin, Volvo Technology AB

Arne Hamann, Robert Bosch GmbH

Daniel Karlsson, Volvo Technology AB

Ulrich Kiffmeier, dSpace GmbH

Stefan Kuntz, Continental Automotive GmbH

Oscar Ljungkrantz, Volvo Technology AB

Mesut Özhan, INCHRON GmbH

# Table of contents

| ΤI  | MMC    | )-2-USE Partners                                           | 2  |

|-----|--------|------------------------------------------------------------|----|

| Αι  | ıthor  | S                                                          | 3  |

| Ta  | able o | of contents                                                | 4  |

| Lis | st of  | Figures                                                    | 5  |

| 1   | Intro  | oduction                                                   | 7  |

| 2   | Star   | ting Point                                                 | 8  |

|     | 2.1    | The TIMMO Methodology                                      | 8  |

|     | 2.2    | The ATESST Methodology                                     | 11 |

| 3   | Ger    | neric Methodology Pattern (GMP)                            | 14 |

|     | 3.1    | Example                                                    | 20 |

|     | 3.2    | Abstracting Timing Properties                              | 27 |

|     | 3.3    | Extending the GMP with Safety Aspects                      | 27 |

| 4   | Inte   | gration of the results of WP2 and WP3 into the methodology | 29 |

|     | 4.1    | TADL2 guides                                               | 29 |

|     | 4.2    | Tool mentors                                               | 30 |

| 5   | App    | lication of the Generic Method Pattern to Use Cases        | 32 |

|     | 5.1    | Integrate reusable component                               | 32 |

|     | 5.2    | Specify timing budgets                                     | 40 |

|     | 5.3    | Specify synchronization timing constraints                 | 49 |

|     | 5.4    | Revise erroneous timing information                        | 54 |

|     |        | 5.4.1 Example: Exceeded time budget                        | 57 |

|     | 5.5    | Exchange models                                            | 64 |

|     |        | 5.5.1 Supplier Side                                        | 64 |

|     |        | 5.5.2 OEM / Integrator Side                                | 67 |

| 6   | Cro    | ss-cutting concerns                                        | 72 |

|     | 6.1    | Specify mode dependent timing information                  | 72 |

| 7   | Cor    | clusion                                                    | 74 |

| 8   | EPF    | Model of the TIMMO-2-USE Methodology                       | 75 |

| 9   | Glos   | ssary                                                      | 76 |

| 10  | Ref    | erences                                                    | 80 |

| Figure 1- The different Phases of the TIMMO Methodology                                                                                                                                                                                                                                                   | 8                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Figure 2 - Different phases and tasks of the TIMMO methodology                                                                                                                                                                                                                                            | 9                    |

| Figure 3 - The structure of the EAST-ADL methodology                                                                                                                                                                                                                                                      | 11                   |

| Figure 4 - TIMMO-2-USE Generic Method Pattern                                                                                                                                                                                                                                                             | 15                   |

| Figure 5: Instantiation of TIMMO-2-USE Generic Method Pattern                                                                                                                                                                                                                                             | 16                   |

| Figure 6 - A simple example to demonstrate the use of the TIMMO-<br>USE Generic Method Pattern                                                                                                                                                                                                            |                      |

| Figure 7 - A simple example to demonstrate the use of the TIMMO-<br>USE Generic Method Pattern and transforming timing requirement<br>between levels of abstraction.                                                                                                                                      | nts                  |

| Figure 8 - The simple example to demonstrate the use of the TIMM 2-USE Generic Method Pattern annotated by timing information                                                                                                                                                                             |                      |

| Figure 9 - A simple example to demonstrate the use of the TIMMO-<br>USE Generic Method Pattern and specifying timing requirements<br>the next level of abstraction                                                                                                                                        | for                  |

| Figure 10 - Abstracting Timing Properties                                                                                                                                                                                                                                                                 | 27                   |

| Figure 11 - Generic Method Pattern applied to functional safety                                                                                                                                                                                                                                           | 28                   |

| Figure 12 - Structure of TADL guides                                                                                                                                                                                                                                                                      | 29                   |

| Figure 13 - Generic methodology applied on integration of a reusal component.                                                                                                                                                                                                                             |                      |

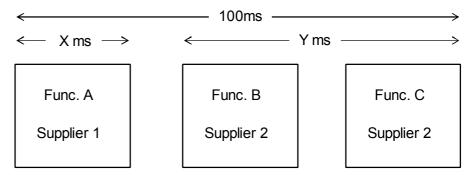

| Figure 14 - Timing behavior before and after integration                                                                                                                                                                                                                                                  | 38                   |

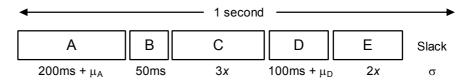

| Figure 15 - The principles of time budgeting                                                                                                                                                                                                                                                              | 41                   |

| Figure 16 - The time budgeting methodology                                                                                                                                                                                                                                                                | 43                   |

| Figure 17 - Example of a budget segment identification strategy                                                                                                                                                                                                                                           | 44                   |

| Figure 18 - Time budgeting example using symbolic time expressio                                                                                                                                                                                                                                          |                      |

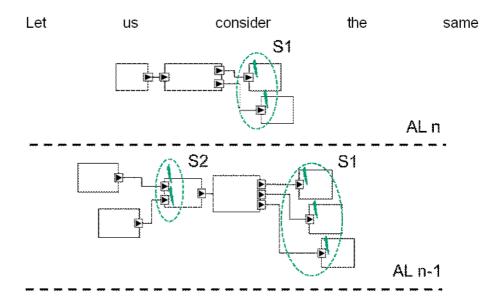

| Figure 18 - Refinement and identification of new sets of events. At tabstraction level $n$ the set S1 is composed by two events. After refinement of the solution at the abstraction level $n$ -1, the set S1 composed by three events, and a new set of events (S2) that must synchronized is identified | the<br>a<br>is<br>be |

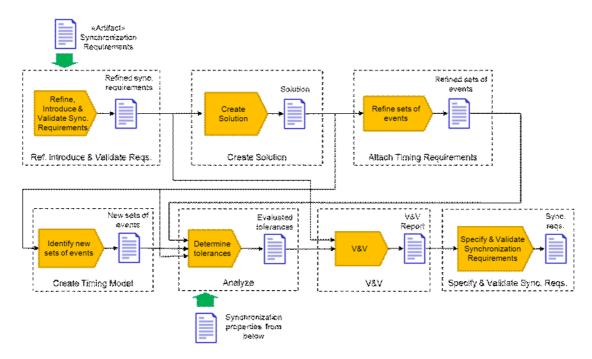

| Figure 19 - Mapping of the specify synchronization constraints into t<br>Generic Methodology Pattern                                                                                                                                                                                                      |                      |

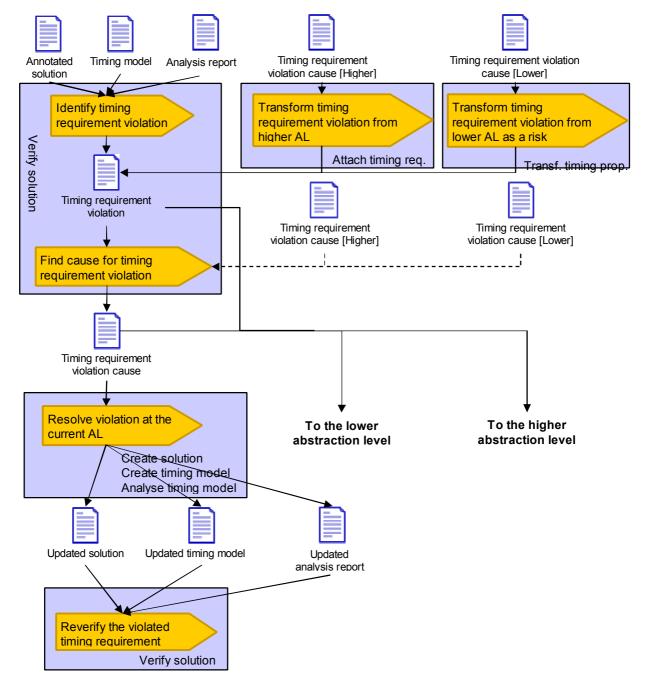

| Figure 21 - Process for the use case Revise erroneous timinformation                                                                                                                                                                                                                                      | _                    |

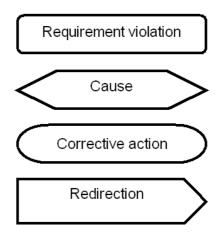

| Figure 22 - Legend for revision charts                                                                                                                                                                                                                                                                    | 58                   |

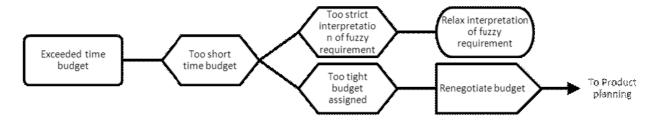

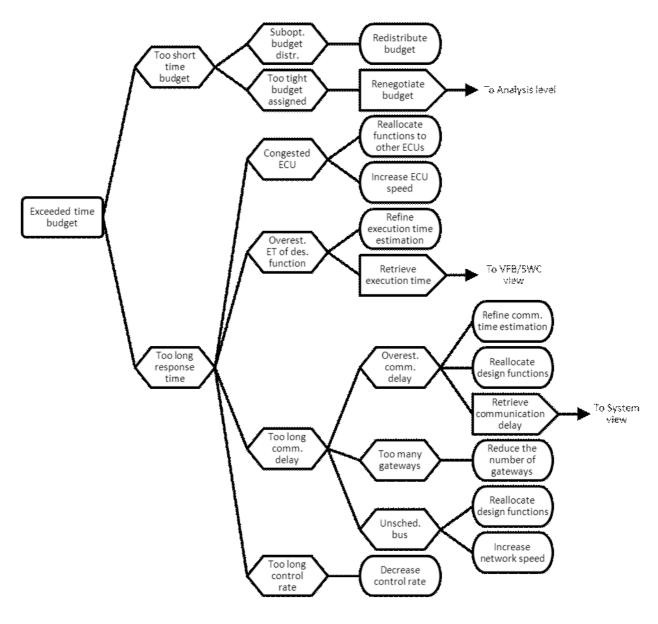

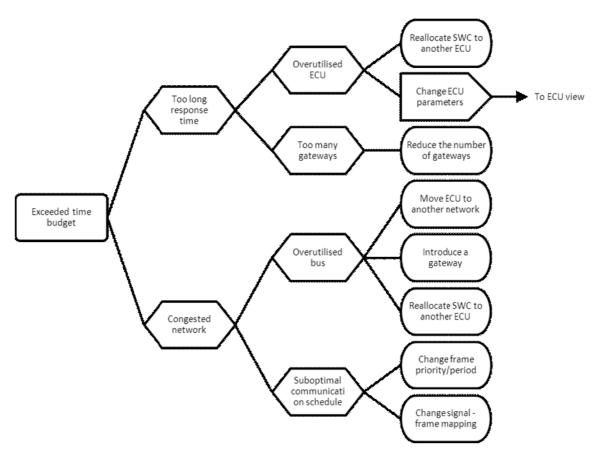

| Figure 23 - Revise exceeded time budget at vehicle level                                                                                                                                                                                                                                                  | 58                   |

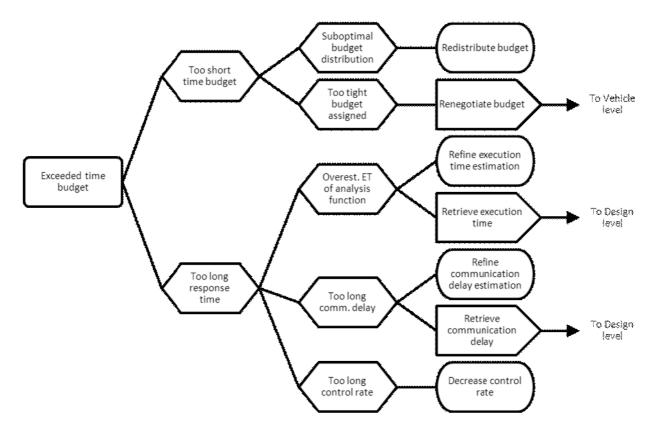

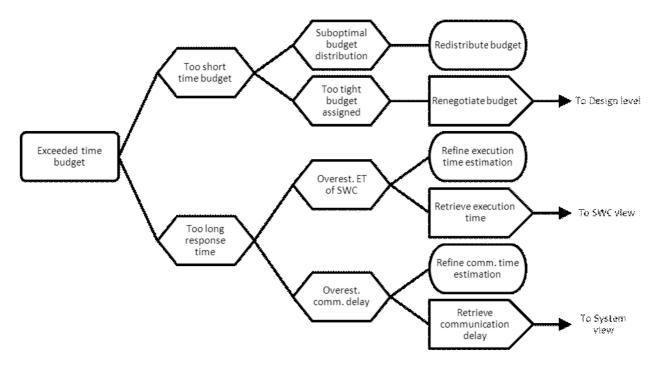

| Figure 24 - Revise exceeded time budget at analysis level                                                                                                                                                                                                                                                 | 59                   |

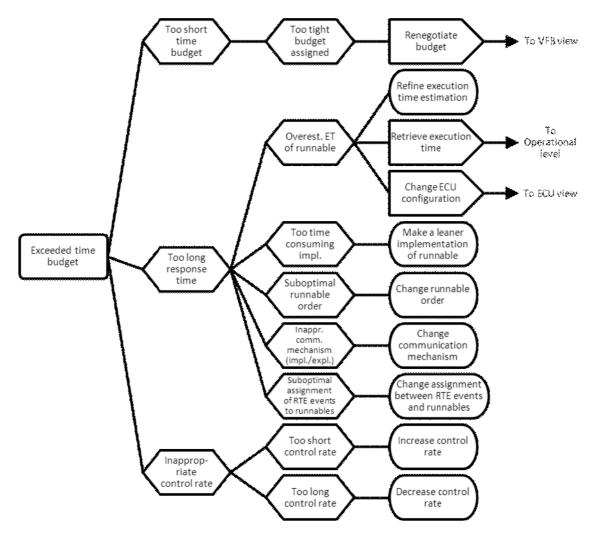

| Figure 25 - Revise exceeded time budget at design level                                                                                                                                                                                                                                                   | 60                   |

| Figure 26 - Revise exceeded time budget in the VFB view      | 61 |

|--------------------------------------------------------------|----|

| Figure 27 - Revise exceeded time budget in the SWC view      | 61 |

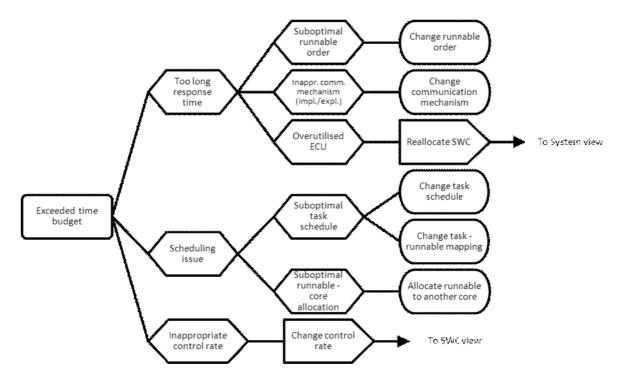

| Figure 28 - Revise exceeded time budget in ECU view          | 62 |

| Figure 29 - Revise exceeded time budget in System view       | 63 |

| Figure 30 - Revise exceeded time budget in Operational level | 63 |

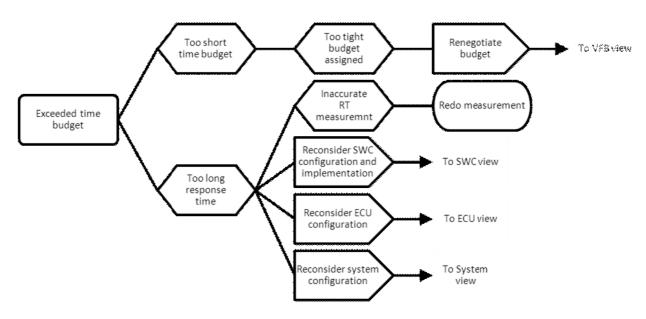

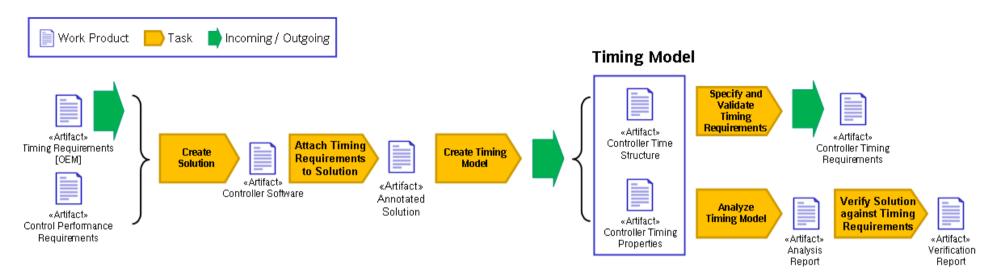

| Figure 31 - Supplier Side of the Exchange Models Use Case    | 65 |

| Figure 32 - OEM Side of the Exchange Models Use Case         | 71 |

In this document the final results of the TIMMO-2-USE methodology are described in detail.

The main goal of the TIMMO-2-USE methodology is to address practical use-cases that require special consideration of timing aspects. Related "timing augmented" methodologies, like the TIMMO and ATESST2 methodologies (see Section 2) do not offer such detail and mainly describe the application of timing analysis and simulation techniques for validation purposes. These aspects are also covered in the TIMMO-2-USE methodology, but additionally it is described how design decisions can be taken based on timing information. In other words, the TIMMO-2-USE methodology introduces a constructive feedback between automotive software system design and real-time systems engineering.

The basis of the TIMMO-2-USE methodology is the *Generic Methodology Pattern (GMP)* described in Section 3. All practical use cases that are described in Section 5 are mapped to this generic methodology. The covered use-cases that are described in Section 5 are the following:

- Integrate reusable component

- Specify timing budget

- Specify synchronization timing constraints

- Revise erroneous timing information

- Exchange models

One important distinctive characteristic of the GMP is the integration of top-down and bottom-up development aspects into one single methodology. Therefore, it is crucial to being able to transform timing information 1) from higher to lower abstraction levels, and 2) from lower to higher abstraction levels. A discussion on how these transformations can be done is given in Section **Error! Reference source not found.**

The GMP general structure was designed with the aim of being applicable to other aspects of software system development apart from timing. To demonstrate this, an extension of the GMP is presented in Section 3.3 that renders it compatible to ISO 26262 compliant safety methodologies.

In order to integrate the results of the technical work packages within TIMMO-2-USE, the concepts of "TADL guides" (Section 4.1) and "Tool mentors" (Section 4.2) were developed for the TIMMO-2-USE methodology.

TADL guides explain the usage of TADL2 (Timing Augmented Description Language 2) concept during the different methodology tasks, whereas Tool mentors link to timing related tools and algorithms that are relevant for the completion of a task at hand.

### 2 Starting Point

In previous projects, software system development methodologies were developed taking into account timing aspects. In the following sections, the most prominent projects and the developed methodologies are shortly presented and related to the TIMMO-2-USE methodology.

### 2.1 The TIMMO Methodology

In the ITEA2 predecessor project TIMMO (TIMing MOdel), a system development methodology was defined explicitly taking into account the real-time behavior of the developed system, an aspect that is ignored in many comparable methodologies.

The TIMMO methodology describes the application of the Timing Augmented Description Language (TADL), that was also developed in the TIMMO project and that is extended in WP2 of TIMMO-2-USE, in the context of the automotive software system development process. Based on the information captured by TADL, the TIMMO methodology highlights the possibilities of applying timing analyses to help the designer taking design decisions and verifying the system's adherence to timing constraints. This guideline on how timing analyses can be applied during the development process of automotive software systems represents the main novelty of the TIMMO methodology.

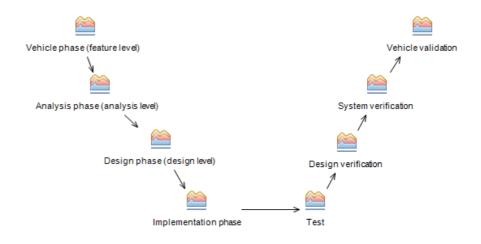

The TIMMO methodology is based on EAST-ADL at the higher levels of abstraction and on AUTOSAR at implementation level (compare Figure 1).

- Vehicle Phase (EAST-ADL)

- Analysis Phase (EAST-ADL)

- Design Phase (EAST-ADL)

- Implementation Phase (AUTOSAR)

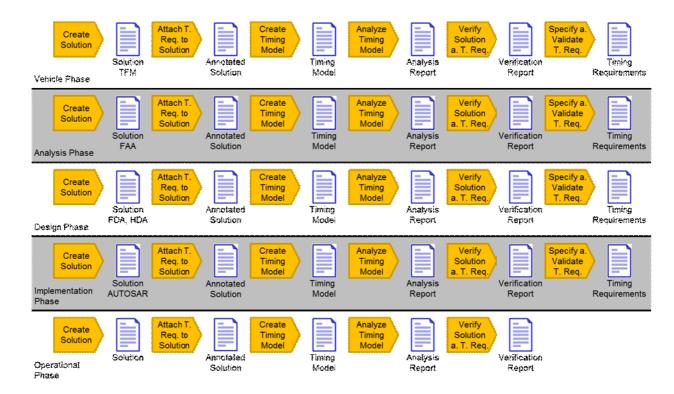

Figure 1- The different Phases of the TIMMO Methodology

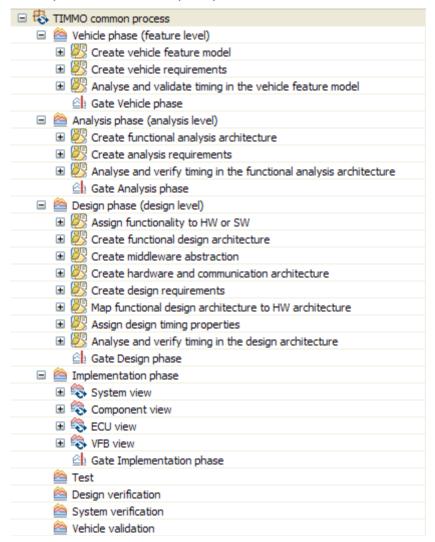

The development steps (*tasks*) that are performed in the different phases of the TIMMO methodology are shown in Figure 2. Please note that the TIMMO methodology allows design iterations at each phase. Each task or sequence of tasks involved in creating the solution in the current phase can be repeated based on the knowledge gained in the timing analysis tasks ("Analyze timing ..."). For this reason, each phase ends with a milestone acting as gateway for checking the real-time behavior of the created solution before continuing system development in the subsequent phase.

Figure 2 - Different phases and tasks of the TIMMO methodology

### Timing Analyses

In the following, the timing analyses that can be performed during the different phases to support the developers in taking design decisions and helping her to ensure the correct real-time behavior are briefly sketched.

#### Vehicle phase

Timing analysis during the vehicle phase focuses on two aspects. First, the logical validation of the timing requirements is performed. This consists in a first (in most cases subjective) evaluation of the general satisfiability of the timing requirements through timing experts.

The second aspect consists in performing consistency checks of the timing requirements.

### **Analysis phase**

During the analysis phase the timing behavior of initial versions of the functional models are checked against the timing requirements formulated at vehicle phase. Additionally, robustness checks are performed to early detect critical paths in the functional architecture that need special focus in the subsequent phases.

### Design phase

During the design phase the first implementation decisions are taken, including the mapping of functionalities to computational resources and utilized communication media. Based on these decisions also many timing properties of the systems are fixed or can be estimated. Therefore, the timing models that can be derived at design phase are much more detailed compared to the previous phases. This enables more detailed timing analyses assessing the approximate dynamic behavior of the software system under development.

At design phase so-called *Response Time Analyses Techniques* can be applied for the first time. They are performed to verify the system's adherence to end-to-end timing requirements. Response time analysis can be performed for a wide range of scopes, spanning from single tasks to complex cause-effect chains involving several ECUs.

### Implementation phase

In the implementation phase all details for accurate timing analyses are available. However, while in the previous phases the results of timing analysis can be used to take design decisions, the focus during the implementation shifts to pure validation, i.e. it is checked in detail if all imposed timing requirements from the previous phases are satisfied.

AUTOSAR defines four different views on the developed software system:

- Virtual Function Bus (VFB) View

- System View

- Component View

- Electronic Control Unit (ECU) View

Each of these views focuses on different aspects, and thus different timing analysis techniques are applied. For instance, on system view the validation of global end-to-end delays, e.g. maximum reaction constraints, spanning several ECUs are of interest. In the case of the ECU view, the focus lies on response time analysis on task level and deadlock analysis for shared resources.

## Relation to the TIMMO-2-USE methodology

The TIMMO methodology is one of the corner stones for the TIMMO-2-USE methodology. The main differences compared to the TIMMO-2-USE methodology are twofold:

- The TIMMO methodology has a pure top-down view on the development process of automotive software systems. In contrast, the TIMMO-2-USE methodology explicitly considers also bottom-up aspects that play an important role for many use cases.

- The TIMMO methodology's main use case lies on the application of timing analyses during the development process.

The TIMMO-2-USE methodology covers many more practical use cases that require the consideration of timing aspects.

Examples include the specification of time budgets, the integration of new functionalities into an existing system, the development of control applications, etc.

### 2.2 The ATESST Methodology

The purpose of the EAST-ADL Methodology, developed in the ATESST2 project, is to give guidance on the use of the EAST-ADL language for the construction, validation and reuse of a well-connected set of development models for automotive embedded software.

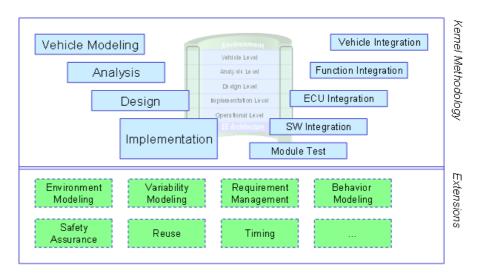

Given the complexity of the development activities in automotive embedded software development, it is mandatory to structure the methodology so as to enable a relatively fast and easy access to the EAST-ADL language for a small kernel of essential development activities which can then be seamlessly extended to a comprehensive treatment of the language including more specialized development activities which may not necessarily be used in any development project. Hence the methodology is structured into two major components, as illustrated in

Figure 3:

Figure 3 - The structure of the EAST-ADL methodology

The main component, the kernel methodology part, comprises a topdown description of the central constructive phases of automotive embedded software development.

The left side of the kernel methodology directly reflects the abstraction levels adopted by EAST-ADL. These phases describe the tasks and

activities that need to be performed on the respective abstraction level in order to efficiently use the language in automotive embedded system development. The implementation phase, however, contains a reference to the AUTOSAR methodology. It therefore only describes how to transit from the design phase to implementation in AUTOSAR.

On the right side, integration and verification and validation is found. The focus in the EAST-ADL methodology is in these phases on the V&V aspects.

The kernel methodology is extended into a comprehensive methodology for automotive development projects by adding three additional and orthogonal activities to each of these phases:

- Specification of V&V cases to be executed and evaluated during the corresponding integration phase. V&V cases are most typically test cases, but can also include reviews etc.

- Verification of the model on a given abstraction level to the requirements of the model at the abstraction level directly above.

- V&V activities on the model artifacts of a given level itself, i.e. peer reviews, consistency checks, check of modeling guidelines etc.

The second main component of the EAST-ADL methodology consists of a set of complementary loosely-coupled extensions to the kernel methodology. Each of these extensions may be used as an add-on to the kernel activities. The following extensions are currently included:

- **Environment Modeling:** Modeling of the (typically analog or discrete-analog) environment of the system to be developed.

- Requirements and V&V: Detailed handling of complex requirements and V&V artifacts.

- Safety Assurance: Development of Safety-critical systems

- **Timing:** Detailed handling of timing requirements and properties.

- Variability Modeling: Detailed handling of variability modeling.

- Behavior modeling: Detailed handling of behavioral modeling

The main idea is that the user of the methodology can compose any set of extensions with the kernel. In order to illustrate the intended correlation and interaction between the extensions, the EAST-ADL methodology presents four different configurations (where a configuration is a set of extensions plus the kernel) of increasing complexity:

- **Core:** Only basic structural models in the kernel methodology.

- Quality: Requirements and V&V extensions are added to Core.

- **Quality+:** Variability, timing, behavior and reuse added to Quality.

- Safety: Safety added to Quality+.

#### The timing extension

All timing aspects, including analysis, are captured in the timing extension. The timing extension contains a simplified and collapsed version of the TIMMO methodology, and has a clear focus on specification of timing constraints in the vehicle, analysis and design phases. The reason is that the analyses indicated in the vehicle and analysis phases of the TIMMO methodology are of relatively informal nature. Detailed timing analysis is not available until a hardware architecture is defined in the design phase. The implementation phase of the EAST-ADL methodology does not contain any timing since AUTOSAR v3.1, to which the methodology interfaces, does not support timing.

The timing extension of the EAST-ADL methodology contains the following tasks:

- Capture Vehicle Timing: End-to-end timing constraints as well as other timing constraints relevant for Vehicle Features are defined.

- Capture Internal Analysis Timing: A budget of delay timing constraints making up end-to-end timing as well as other timing constraints constraining elements inside the FunctionalAnalysisArchitecture are defined.

- Capture External Analysis Timing: End-to-end timing constraints as well as other timing constraints on external input and outputs are defined

- Assess Timing Feasibility: Consistency of timing constraints and feasibility of meeting timing constraint under a chosen DesignArchitecture is assessed.

- Capture External Design Timing: End-to-end timing constraints as well as other timing constraints on external input and outputs are defined.

- Capture Internal Design Timing: A budget of delay timing constraints making up end-to-end timing as well as other timing constraints constraining elements inside the FunctionalDesignArchitecture are defined.

## Relation to the TIMMO-2-USE methodology

The EAST-ADL methodology addresses all aspects of the automotive EE development process, whereas the TIMMO-2-USE methodology focuses on a certain set of use cases related to timing that are mapped to a Generic Methodology Pattern (GMP), see Section 3. The GMP summarizes all tasks in all extensions (except timing) of the EAST-ADL methodology in one task: Create solution. The tasks in the timing extension correspond to the other tasks in the GMP. However, such mapping is not straight-forward and will result in a many-to-many relation.

This chapter describes the TIMMO-2-USE Generic Method Pattern GMP. This method pattern is the basis for all steps to be taken during the course of a phase and level of abstraction respectively.

### **Important Assumptions**

The following assumptions shall be kept in mind when reading the following paragraphs:

- 1. All tasks can be repeated an arbitrary number of times.

- 2. A sequence of tasks can be repeated an arbitrary number of times.

- 3. A role or roles performing a task have access to all artifacts that are a) available at the beginning of a phase, and b) created by tasks during the course of the phase. For all details about the work product dependencies refer to the EPF model [4].

- 4. The term "Timing Property" is used in such a way that it refers to the timing property type *and* its value.

#### Introduction

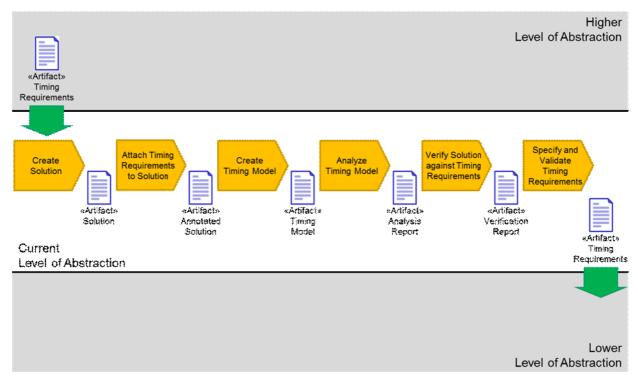

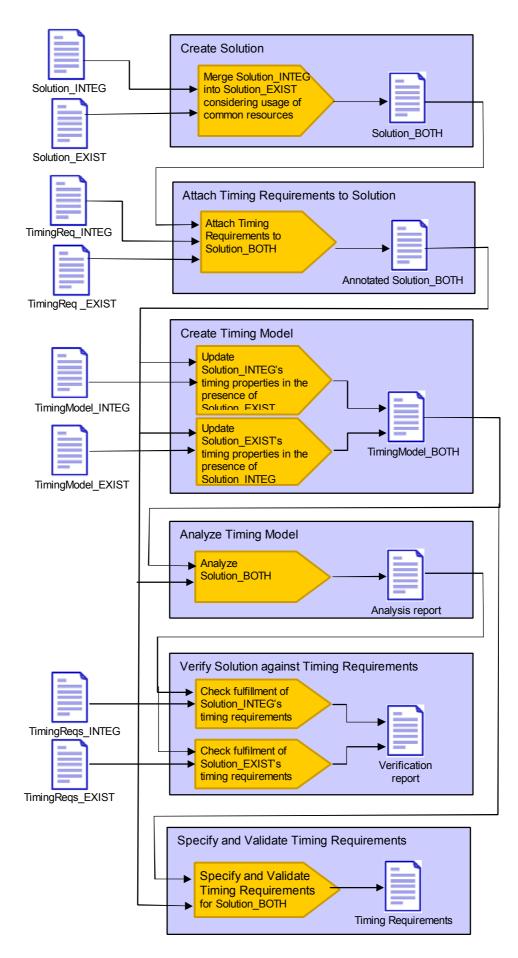

As shown in Figure 4, the TIMMO-2-USE Generic Method Pattern consists of the six tasks called "Create Solution", "Attach Timing Requirements to Solution", "Create Timing Model", "Analyze Timing Model", "Verify Solution against Timing Requirements", and "Specify and Validate Timing Requirements". In essence, these tasks have the following purposes:

- "Create Solution" describes the definition of the architecture without any timing information.

- "Attach Timing Requirements to Solution" describes the formulation of timing requirements in terms of the current architecture.

- "Create Timing Model" describes the definition of a formalized model for the calculation of specific timing characteristics based on properties of the current architecture.

- "Analyze Timing Model" describes the actual execution and evaluation of all necessary "calculations" according to the timing model.

- "Verify Solution against Timing Requirements" describes the comparison of the obtained analysis results with the specified timing requirements.

- "Specify and Validate Timing Requirements" describes the identification of mandatory timing characteristics and their promotion to timing requirements for the next development phase.

Please note that for the GMP to be compatible with safety methodologies according to ISO 26262, another task "Refine, Introduce & Validate Requirements" was introduced. This task, however, is treated separately in Section 3.3. Here, only those tasks of the GMP that are relevant for timing considerations are discussed.

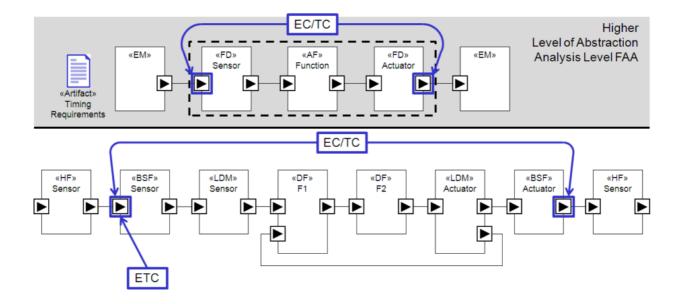

By and large, these tasks are carried out at every level of abstraction of the EAST-ADL. Since the EAST-ADL, as well as TIMMO-2-USE, defines a phase for every level of abstraction these tasks are carried out for every level of abstraction: Vehicle, Analysis, Design, Implementation and Operational Level. As shown in Figure 5 there are two exceptions: The first exception is that at the beginning of the Vehicle Phase, a formal work product "Timing Requirements" is not available. The second exception is that at the end of the Operational Phase the task "Specify and Validate Timing Requirements" is not carried out.

Figure 4 - TIMMO-2-USE Generic Method Pattern

#### Instantiation

As already indicated in the previous paragraph the TIMMO-2-USE Generic Method Pattern can be applied on all levels of abstraction defined by the EAST-ADL.

Figure 5: Instantiation of TIMMO-2-USE Generic Method Pattern

This instantiation is shown in Figure 5. In every phase of the methodology the corresponding tasks are conducted — except the "Specify and Validate Timing Requirements" in the Operational Phase. At the end of the Vehicle-, Analysis-, Design-, and Implementation Phase the work product "Timing Requirements" is passed to the following phase as basis for subsequent activities in that phase — except at the end of the Operational phase.

In the following, all tasks and their purpose are described in more detail. The tasks are described in the order as they appear in Figure 4 (from left to right).

#### Create Solution

Based on the given requirements<sup>1</sup>, including timing requirements, that originate from the higher level of abstraction respectively previous phase, a solution is created or an already existing solution is revised. While creating/revising the solution the given timing requirements must be considered. In other words the given timing requirements, like any other non-timing requirement, guide the creation of the solution. The resulting solution is captured in appropriate models. In case of EAST-ADL these models are the Technical Feature Model TFM on the Vehicle Level, Functional Analysis Architecture FAA on the Analysis Level, Functional Design Architecture FDA and Hardware Design Architecture HDA on the Design Level, and Environment Model EM

A solution created on the higher level of abstraction respectively in the previous phase, is considered as requirement – a set of requirements – as well.

which is present on all levels of abstraction. Out of these, the first three models primarily capture timing requirements and properties related to the system's application. The Hardware Design Architecture provides parameters for execution and hardware delays. The Environment Model provides characteristics and constraints imposed by the surrounding systems.

Several solutions (alternatives) can evolve from the task "Create Solution" and each of those solutions shall have the potential to satisfy the given requirements. However, each solution may result from specific design decisions that have been taken during the course of this task.

# Attach Timing Requirements to Solution

Based on the created solution the timing requirements are formulated in a way that is suitable for further processing on the current level of abstraction. Timing requirements that are carried over from a previous phase must be transformed and attached to the solution architecture accordingly, such that they are "compatible" with the timing model (and the timing properties) on the current level of abstraction.

In a nutshell: Timing requirements are expressed using events, event chains, and timing constraints that are imposed on these events and event chains. Events refer to locations, usually ports, in a solution model at which the occurrences of the events are observed; while event chains specify a causal relationship between events and their temporal occurrences. During every phase, a solution model is created based on the requirements and on the solution model created in the previous phase. An event specified in the previous phase referring to an observable location in the corresponding solution model possibly has to be transformed or mapped into an event referring to an observable location in the solution model created during the current phase. This transformation has to be performed for all events and event chains, and especially the *values* of the timing requirements imposed on event chains.

This task must be performed for every alternative solution that evolve from the task "Create Solution".

#### **Create Timing Model**

Once the solution has been created and the timing requirements have been attached in a way that suits the current level of abstraction, a timing model for this solution is created.

The timing model defines how – based on the timing properties of the solution – specific timing analysis methods can be applied, in order to predict / calculate the dynamic behavior of the solution and the timing characteristics (e.g. the WCRT of a control function) emerging from it.

The timing properties required by the various timing analysis methods need to be determined and assessed. The methods applied to determine the particular values are manifold: expert knowledge and estimation, knowledge from previous projects or iterations within the current project, formalized analysis, simulation, etc. In addition, the methods being used may vary depending on the phase: On higher levels of abstraction other methods are used than on lower levels. For example, scheduling analysis is used on implementation level, but not on vehicle level.

The most appropriate and suitable method should be selected for this purpose.

Note that the purpose of this task is not to define new types of timing analysis methods or timing properties, but to decide how these can be practically used to describe the dynamic behavior of the solution.

This task must be performed for alternative solutions that evolve from the task "Create Solution". And with regard to the dynamic behavior of the solutions there may be different timing models leading to different sets of timing properties and their values.

### **Analyze Timing Model**

Depending on the specifics of the timing model and the different timing analysis methods which are applied, all necessary calculations are executed and their results – looking at the whole picture and the target system – are evaluated.

It may happen that several alternative solutions are available, and in this case the purpose of the task "Analyze Timing Model" is to identify and quantify the strengths of every solution with regard to the dynamic – temporal – behavior. One can select the most appropriate and/or promising solutions in order to proceed with the development.

# Verify Solution against Timing Requirements

In order to answer the question – does the solution satisfy the given timing requirements – the values of the timing properties obtained by the analysis are compared against the values of the requirements attached to the solution.

The primary purpose of this task is to decide whether to continue conducting the subsequent tasks in the development process, or to repeat any or a sequence of previous tasks. In other words at this point it is decided "whether the numbers are good enough for progressing", or whether those numbers have to be revised (iteration). It could also happen that the solution subject to timing analysis must be revised, or even worse, a new solution must be searched.

If several alternative solutions are available then the purpose of the task "Verify Solution against Timing Requirements" is to verify the timing properties of every solution. Eventually, one has to select the most appropriate solution – one solution – in order to proceed with the development.

Milestone: Quality Gate

At a quality gate, which is not shown in the given figures, immediately following the task "Verify Solution against Timing Requirements" the results of the verification are checked, and a decision is taken to either continue or repeat the phase. Of course, if the quality gate is negative the necessary actions depend on the kind of defect detected. For example, sometimes it would only be necessary to repeat a specific or a number of tasks, rather than all tasks in the phase.

# Specify and Validate Timing Requirements

Once the quality gate has been passed all or some of the obtained timing properties and transformed timing requirements are converted into corresponding timing requirements.

The result of the task is *not* that *all* timing properties that were found in the previous tasks are converted into timing requirements, but only those of them which are fundamental and important for design decision to be taken in subsequent steps. One criterion for identifying timing properties as timing requirements is that they were critical for the verification performed.

These timing requirements are the basis for any design work being conducted during the next phase.

### 3.1 Example

This section introduces a very simple example that is used to explain how the Generic Method Pattern is applied respectively utilized. In particular, it describes how the Generic Method Pattern is applied on the Design Level.

#### Example - Introduction

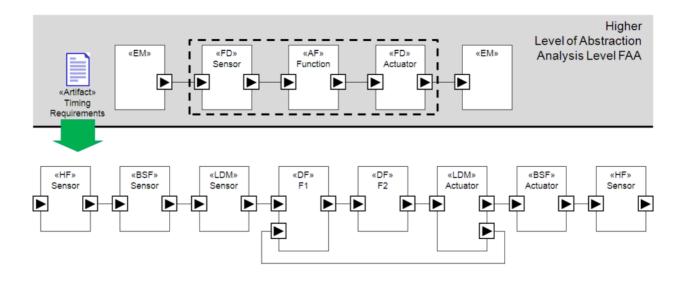

At the beginning of a phase the solution and the corresponding timing requirements are available from the previous phase respectively higher level of abstraction – the Analysis Level. This solution is shown in the upper part of Figure 6. The solution consists of two functional devices («FD») and one function/component («AF»). One of the functional devices, the one on the left-hand side in the figure, represents the sensor and the other functional device, the one on the right-hand side in the figure, represents the actuator. The purpose of the functional device named "Sensor" is to provide data from the environment to the E/E system to be developed; while the purpose of the functional device called "Actuator" is to "control/impact" the environment. The [analysis] function/component («AF») called "Function" processes the data received from the environment via the functional device "Sensor" and controls/impacts the environment via the functional device called "Actuator".

In the artifact "Timing Requirements" attached to the solution one event chain is specified. This event chain and the timing constraint are depicted by the blue colored event chain drawn above the function/component called "Function" in Figure 7. The event chain references an event and its occurrence can be observed at the required port of the functional device called "Sensor". This event is playing the role of the stimulus. The event chain references a second event and its occurrence can be observed at the provided port of the functional device called "Actuator". This event is playing the role of the response.

A ReactionConstraint (TC) is imposed on this event chain (EC) and its value is 125 ms including a variation – jitter – of 30 ms yielding in a time range of 110 ms to 140 ms.

| Scope                           | ReactionConstraint     | Minimum | Maximum |

|---------------------------------|------------------------|---------|---------|

| Sensor - Function<br>- Actuator | 125 ms, -15 ms, +15 ms | 110 ms  | 140 ms  |

# Example – Create Solution

On the current level of abstraction – in the current phase – a solution is created by performing the task "Create Solution". The created solution is supposed to satisfy the given functional and non-functional requirements, specifically the timing requirements.

The solution is shown in the lower part of Figure 6. It consists of two Hardware Functions («HF»), two Basic Software Functions («BSF»), and two Logical Device Managers («LDM»): one called "Sensor" and the other called "Actuator". Additionally, two [design] functions/components («DF») called "F1" and "F2" are part of the system architecture. The combination on the left hand side in the figure corresponds to the sensor, and the combination on the right hand side corresponds to the actuator. The two [design] functions/components («DF») called "F1" and "F2" processing the data received from the environment via the HF, BSF and LDM, and control/impact the environment via the LDM, BSF, and HF. The Logical Device Manager "Actuator" provides additional data to the function/component called "F1".

Current Level of Abstraction Design Level FDA

Figure 6 - A simple example to demonstrate the use of the TIMMO-2-USE Generic Method Pattern

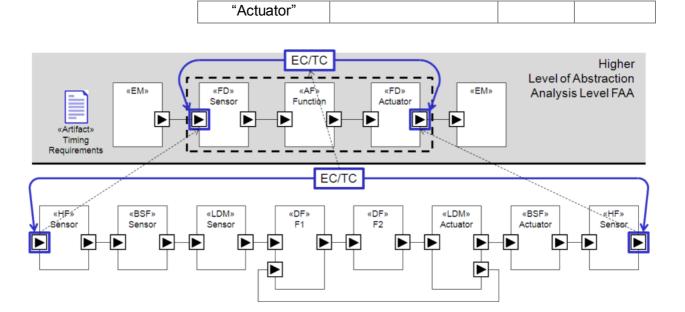

# Example – Attach Timing Requirements to Solution

The timing requirements originated from the previous phase, the Analysis Phase, are transformed into timing requirements that correspond with the solution created in the current phase, the Design Phase. In the example the given timing requirement, the event chain and timing constraint in the upper part of Figure 7, are transformed into an event chain with corresponding timing requirement that is imposed on the current phase's solution.

The result of the transformation is

| Scope          | Latency Timing<br>Constraint | Minimum | Maximum |

|----------------|------------------------------|---------|---------|

| HF "Sensor" HF | 125 ms, -15 ms, +15 ms       | 110 ms  | 140 ms  |

Current Level of Abstraction Design Level FDA

Figure 7 - A simple example to demonstrate the use of the TIMMO-2-USE Generic Method Pattern and transforming timing requirements between levels of abstraction.

Observation: On the first view it seems obvious that the event chain/timing constraint specified on the higher level of abstraction (Analysis Level) is transformed in a one-to-one manner to an event chain/timing constraint on the current level of abstraction (Design Level). And a valid question is whether this timing requirement shall be transformed at all.

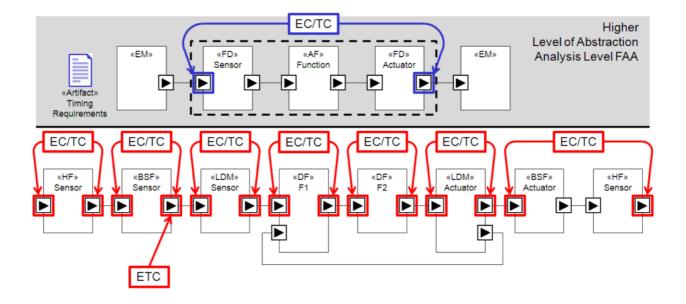

# Example – Create Timing Model

During the course of the task "Create Timing Model" the solution is annotated with events, event chains, and timing constraints as shown in the lower part of Figure 8 – depicted by the red colored event chain drawn above every element of the solution. On this level of abstraction the given event chain including its latency timing constraint is broken down into seven subsequent event chains, playing the role of event chain segments, and latency timing constraints are imposed on those seven event chains respectively event chain segments. In addition a periodic event triggering constraint is imposed on the event that is observed at the provided port of the basic software function called "Sensor", because the solution provides data for example periodically.

In this example, an event chain referring to the second provided port of logical device manager called "Actuator" and the second required port of the [design] function/component called "F1" is not specified, because this path is considered unimportant with regard to timing. Note that in other cases this path could possibly have a significant impact on the dynamic behavior of the system, e.g. in a control application, and then must be considered accordingly.

Current Level of Abstraction Design Level FDA

Figure 8 - The simple example to demonstrate the use of the TIMMO-2-USE Generic Method Pattern annotated by timing information

Furthermore, an event chain is specified referring to an event that is observed at the required port of the hardware function called "Sensor", and to an event that is observed at the provided port of the hardware function called "Actuator". On that event chain a timing constraint is imposed. This timing constraint – the property and the value – may be the same as the given one [timing requirement].

The values of all those timing properties are determined, too, and for good reasons one could specify the following latency timing constraints:

- 1. A latency timing constraint imposed on the combination HF, BSF, and LDM called "Sensor" of 30 ms including a variation of -2 ms and +5 ms resulting in a time range of 28 ms to 35 ms.

- 2. A latency timing constraint imposed on the function/component called "F1" of 20 ms including a variation of -1 ms and +2 ms resulting in a time range of 19 ms to 22 ms.

- 3. A latency timing constraint imposed on the function/component called "F2" of 45 ms including a variation of -5 ms and +3 ms resulting in a time range of 40 ms to 48 ms.

- 4. A latency timing constraint imposed on the combination LDM, BSF, and HF called "Actuator" of 25 ms including a variation of -2 ms and +10 ms resulting in a time range of 23 ms to 35 ms.

The following table summarizes the values of all determined latency timing constraints.

| Component                  | Latency Timing Constraint | Minimum | Maximum |

|----------------------------|---------------------------|---------|---------|

| HF, BSF, LDM<br>"Sensor"   | 30 ms, -2 ms, +5 ms       | 28 ms   | 35 ms   |

| F1                         | 20 ms, -1 ms, +2 ms       | 19 ms   | 22 ms   |

| F2                         | 45 ms, -5 ms, +3 ms       | 40 ms   | 48 ms   |

| LDM, BSF, HF<br>"Actuator" | 25 ms, -2 ms, +10 ms      | 23 ms   | 35 ms   |

|                            | Totals:                   | 110 ms  | 140 ms  |

Additionally, the value of the periodic event triggering constraint that is imposed on the event observable at the provided port of the basic software function called "Sensor" is 10 ms including a variation – jitter – of 2 ms resulting in a time range of 8 ms to 12 ms.

# Example – Analyze Timing Model

In this step – carrying out the task "Analyze Timing Model" – the values of the timing properties specified are scrutinized.

In the example, executable models that are available for every component are used to perform simulations in order to analyze the timing behavior of the given solution. During the simulations it turns out that the function/component "F1" tends to have a slightly larger response time than specified during the task "Find Timing Properties" – typically 5 ms – which leads to a variation of +8 ms.

Further analyses show that the assumptions made during the task "Create Timing Model" with regard to the dynamic behavior of the interconnect between "Actuator" and "F1" were not correct. It turns out that the variation of the response time is not as large as presumed before. Continuing simulations lead to the fact that the latency timing constraints can be adjusted accordingly; in this case the variation is not more than +2 ms.

Table 1 summarizes the values of all determined latency timing constraints.

| Component                  | Latency Timing Constraint | Minimum | Maximum |

|----------------------------|---------------------------|---------|---------|

| HF, BSF, LDM<br>"Sensor"   | 30 ms, -2 ms, +5 ms       | 28 ms   | 35 ms   |

| F1                         | 20 ms, -1 ms, +8 ms       | 19 ms   | 28 ms   |

| F2                         | 45 ms, -5 ms, +3 ms       | 40 ms   | 48 ms   |

| LDM, BSF, HF<br>"Actuator" |                           |         | 27 ms   |

|                            | Totals:                   | 110 ms  | 138 ms  |

Table 1: New values of the latency timing constraints after performing timing analyses on the given solution

Example – Verify Solution against Timing Requirements

The obtained values of the timing properties are now compared against the given timing constraint transformed from the higher level of abstraction.

Alternative #1: For this purpose, an event chain is specified that references the event observable at the required port of the hardware function called "Sensor", playing the role "Stimulus", and that references the event observable at the provided port of the hardware function called "Actuator", playing the role "Response".

Alternative #2: For this purpose, an event chain is specified that references the event observable at the required port of the basic software function called "Sensor", playing the role "Stimulus", and that references the event observable at the provided port of the basic software function called "Actuator", playing the role "Response".

This event chain and the timing constraint imposed on it are depicted by the blue colored event chain shown in the bottom part of Figure 9. A latency timing constraint is imposed on this event chain and the value of this latency timing constraint is as follows:

| Latency Timing Constraint | Minimum | Maximum |

|---------------------------|---------|---------|

| 120 ms, -10 ms, +18 ms    | 110 ms  | 138 ms  |

A comparison of this timing property of the solution with the given one mentioned in the introduction of the example shows that the solution satisfies the given timing constraint respectively latency timing constraint; 110 to 138 ms versus 110 to 140 ms.

Example – Specify and Validate Timing Requirements

As a formal step the determined timing property – latency timing constraint – and its value – 110 ms to 138 ms – are declared as timing requirement/constraint which shall be considered in the next phase, in particular when carrying out the task "Create Solution" in the following phase. Note, that the timing properties, associated with every functional device and function/component, are not converted into timing requirements.

Current Level of Abstraction Design Level FDA

Figure 9 - A simple example to demonstrate the use of the TIMMO-2-USE Generic Method Pattern and specifying timing requirements for the next level of abstraction.

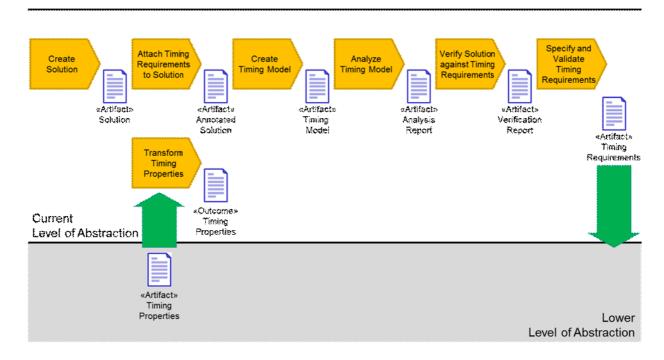

### 3.2 Abstracting Timing Properties

This sub-section describes the idea of "Abstracting Timing Properties" on a lower level of abstraction in order to use them on a higher level of abstraction. The results of this abstraction are used as additional (optional) input work product for the task "Create Timing Model".

Figure 10 shows a simplified view of the methodology with regard to this approach. The task "Transform Timing Properties" on the current level of abstraction transforms the timing properties' values of a solution created on the lower level of abstraction into values of timing properties that are used at the current level of abstraction. The transformed timing properties, including their values, are an optional input work product for the task "Attach Timing Requirements to Solution" conducted on the current level of abstraction. The idea behind this is that values of timing properties that are obtained during later phases of the development process can be used on higher levels of abstraction respectively in earlier phases of the development process. This is an important capability in order to support iterative development processes.

Figure 10 - Abstracting Timing Properties

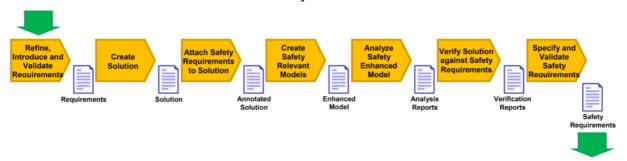

### 3.3 Extending the GMP with Safety Aspects

The GMP general structure was designed with the aim of being applicable to other aspects of the E/E development as well, not only timing. To demonstrate and validate this, it has been applied to functional safety according to ISO 26262 in cooperation with the TimeSafe project.

When investigating ISO 26262, the need to refine requirements at the current abstraction level before the actual solution is created and modeled, was manifest. In particular, ISO 26262 explicitly requires the technical safety requirements (design level) to be specified before the system design is created and the hardware and software safety requirements (implementation level) to be specified before the hardware and software design is created. For this reason the first task "Refine, Introduce and Validate Requirements" was introduced. The seven tasks of the GMP applied to safety are shown in Figure 11 and the first task is briefly described as follows.

Figure 11 - Generic Method Pattern applied to functional safety

# Refine, Introduce & Validate Requirements

In this task, the *requirements* from previous/upper abstraction level are refined and complemented to this abstraction level. This means that some assumptions on the design are made on this abstraction level. Typically the requirements introduced or refined in this work task are later refined and/or formalized when the design has been made. For functional safety, the functional, technical, hardware or software safety requirements are introduced in this work task and allocated to the design and detailed in later work tasks, thus creating the functional/technical safety concept or being part hardware/software design. The refined and introduced requirements are also *validated*. This means that the requirements are checked to be consistent and corresponding to the actual expectations (intended requirements) of the stakeholders.

### 4 Integration of the results of WP2 and WP3 into the methodology

In order to integrate the results of the other technical work packages into the TIMMO-2-USE methodology, the concepts of "TADL guides" and "Tool mentors" were developed in joint effort with work packages 2 and 3.

TADL guides explain the usage of TADL2 concept during the different methodology tasks, whereas Tool mentors link to tools and algorithms that are relevant for the completion of the task at hand.

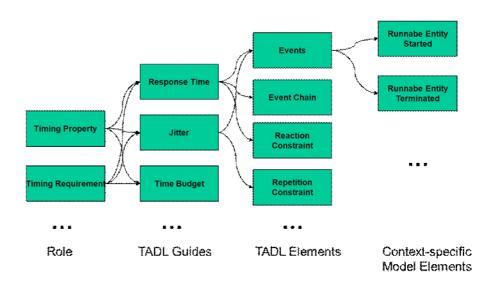

### 4.1 TADL2 guides

A TADL guide describes which language elements can be used in a specific task of the TIMMO-2-USE methodology to describe timing information. TADL guides, therefore, represent a link between the technical results of the work packages 2 (Language) and 4 (Methodology).

Figure 12 - Structure of TADL guides

Figure 12 shows the overall structure of the TADL guides. Basically, each TADL guide can be interpreted either as timing property or as timing requirement depending on the role it is referenced in. Then, there is the actual description of the TADL2 language concept. Examples for TADL guides that were created are:

- Execution time (Worst-case, Best-case, Simulated, Measured)

- End-to-end Latency

- Sampling Rates

- Time Budget

- Response Time

- Communication Delay

- Slack

- Repetition pattern

- Synchronization

Each TADL guide references the TADL elements, i.e. classes of the TADL2 meta-model, that are necessary to use the TADL guide. Examples are events, event chains, etc.

In order to maximize the usefulness of the TADL guide, the guide for the same TADL2 concept is instantiated for each abstraction level it is applicable for. Additionally, each TADL guide is completed with context specific model elements, like the list of relevant EAST-ADL and AUTOSAR events, and a context specific example.

The concrete TADL guides are not included in this deliverable. They can be found in the EPF version of the TIMMO-2-USE methodology.

#### 4.2 Tool mentors

A Tool mentor describes which algorithm or tool can be used in a specific task of the TIMMO-2-USE methodology to solve a specific timing-related problem at hand. Tool mentors, therefore, represent a link between the technical results of the work packages 3 (Tools & Algorithms) and 4 (Methodology). Tool mentors give *precise* hints on the possibilities to apply tools and algorithms to solve specific problems depending on the context. Therefore, for each considered tool or algorithm, different Tool mentors for each relevant combination of abstraction level and methodology task were created.

All tool mentors for the tools and algorithms developed in the TIMMO-2-USE project were created using the following template:

- Abstraction level: Abstraction level the Tool mentor can be applied to. If a tool/algorithm can be applied on various abstraction levels a separate Tool mentor was created for each abstraction level

- 2. *Use Cases*: Main use cases of TIMMO-2-USE for that the Tool mentor can be applied.

- Covered aspect: Kind of timing information that is delivered by the tool/algorithm, like for instance worst-case execution time (WCET)

- 4. Algorithm: Detail on the underlying formalism and technique

- 5. *Inputs*: Details on the required input data like, for instance, source code, binary code, etc.

- 6. Particular constraints on inputs

- 7. *Preparation of input*: Explanation of ways on "How to get the data ready for applying the algorithm".

- 8. Invocation of the algorithm: Hints on how to use the tool

- 9. Outputs: Kind and quality of results delivered by the tool / algorithm

- 10. *Visualization of results*: Information on how the output can be assessed, e.g. textual report, graphical visualization, etc.

The concrete Tool mentors are not included in this deliverable. They can be found in the EPF version of the TIMMO-2-USE methodology or in D12.

### 5 Application of the Generic Method Pattern to Use Cases

In this section the application of the GMP to the covered main use cases, identified within the TIMMO-2-USE project, is conducted. For each main use case a different instance of the GMP was created, giving details on all timing related activities. The different use cases are additionally modelled with SPEM (Software Process Engineering Metamodel) using EPF (Eclipse Process Framework). This version can be found under [4].

### 5.1 Integrate reusable component

#### Problem statement

In the context of the automotive industry, an OEM offers a range of vehicles marketed in different classes which provide different extents of functionalities related to safety, comfort, or similar criteria. Caused by marketing tendencies and proceedings in technology, vehicles are being enriched by new functionalities either newly invented or taken over from higher class vehicles. In that case new functionalities are integrated step-wise into an existing system during the development phase. Similar integration problems arise when a new platform generation is being developed and functions are moved from one ECU to another.

Usually, new functionalities cannot be introduced independently of the existing system's functionalities due to interference with the existing system's ECU resources and communication network.

Changing a system's architecture necessarily changes its behavior with respect to timing. For instance, end-to-end latencies might increase due to additional preemptions of tasks or arbitration of bus messages.

This use case addresses the challenges which arise during the process of integration.

#### Overview

In the following, the focus will be on the Design phase but similar considerations apply to the Implementation phase, i.e the workflow tasks are basically the same.

The integration may cover one or more ECUs including their communication paths. We assume that one or several target ECUs onto which the design function in question shall be integrated has been selected. The actual ECU selection process is not covered by this use case. However, there are several aspects that must be considered when choosing the target ECU(s), like for instance the targeted functional domain (e.g. body controller), the physical location (e.g. near front wheels), or the availability of input signals (e.g. sensor signals, buses), etc.

The investigations on the use case "Integrate Re-usable Component" assume that the software system executed on the target ECU(s),

which the design function is to be integrated into, was developed according to the Generic Methodology Pattern (see Section 3). This means, that the model contains all components necessary for fulfilling the system's functionality, and all timing properties of the components are known and described.

The use case considers two integration scenarios:

A) Adding a legacy design function:

Here it is assumed that the legacy design contains TADL2 compliant timing information.

B) Developing and adding a new design function:

For scenario B, there are two approaches are distinguished:

- B1) Developing the new design function stand-alone without taking into account interactions with the target system. In this case a separate model is created for the new design function including timing information. In a second step this new model is merged into the existing one as in scenario A.

- B2) Developing the new design function directly into the existing model explicitly taking into account interactions with the target system.

Approach B1 includes the development of a new functionality from scratch. It handles timing information according to the GMP resulting in a stand-alone solution. This stand-alone solution would then have to be integrated into the existing solution which is identical to scenario A.

In the remainder of this section, the scenarios A and B1 are discussed. The focus lies, thus, on the integration of one EAST-ADL model into another, both models already containing timing information.

The further discussions refer to the *Design* phase. They can also be applied to the *Implementation* phase. During the *Vehicle* and *Analysis* phases, models consist of pure functional components where end-to-end delays are composed by chaining budget segments of the components, and resources are considered to be infinite. Consequently, integration effects cannot be investigated during those phases. In contrast, during the *Design* phase components are declared to be realized in hardware or software resulting in a Hardware Design Architecture (HDA) and a Functional Design Architecture (FDA). On this level, and on the lower *Implementation* level, the integration aspect can be investigated, i.e. the interference of components due to competition for common resources.

# Mapping to Generic Methodology Pattern

Figure 13 illustrates the integration process, and how it maps to the GMP presented in Section 3.

In the following paragraphs, the existing system which the design function is integrated into is referenced with the suffix \_EXIST (e.g. Solution\_EXIST) while the design function to be integrated is referenced with the suffix INTEG (e.g. Solution INTEG). The final

system including both solutions is referenced with the suffix  $\_BOTH$  (e.g. Solution $\_BOTH$ ).

Figure 13 - Generic methodology applied on integration of a reusable component.

#### Create Solution

When performing the task *Create Solution*, the components of Solution\_EXIST and Solution\_INTEG have to be brought together to become Solution\_BOTH. From the functional perspective, the solutions still may co-exist in the resulting model as long as no functional synergy is detected. This also implies that both solution topologies including inter-component communication may remain unchanged. However, it will often be a design goal to search for synergies in order to provide cost-efficient solutions. Therefore, reuse of input/output ports and network messages is advised, e.g. in case both solutions use the same sensor signal, or a required signal is already available on another ECU.

# Attach Timing Requirements to Solution

It is assumed that the resulting Solution\_BOTH will contain the same events like the previous Solution\_EXIST and Solution\_INTEG, so that all timing requirements applied on the previous solutions persist in Solution\_BOTH. If functional synergy is exploited in Solution\_BOTH, then some requirements will refer to common event chain segments indicating timing dependencies.

### **Create Timing Model**

At first, a timing model is created for Solution\_BOTH as described in the GMP. Large parts of this timing model may be adopted from the previous solutions without modification. As described above, some parts of the previous timing models may overlap, if functional synergy is exploited, i.e. two events from the previous solutions are merged into one and the resulting event chains have common segments. If for example, a sensor signal is reused as a common resource in Solution\_BOTH, then the segments of a timing event chain have to be adapted, but the requirement for the end-to-end latency is the same.

The following two subtasks are described in more detail:

- 1) Update \_INTEG's timing properties,

- 2) Update EXIST's timing properties.

The focus in subtask 1 is on updating the timing properties of Solution\_INTEG, like WCET of functions. This is necessary, since usually the target system already accommodating Solution\_EXIST is different from the system which Solution\_INTEG was developed on. There might be different ways of updating the timing properties. For instance, for worst-case execution times the following approaches are possible:

• Transforming Solution\_INTEG's timing properties from the old to the new hardware/software design architecture.

One possible method here is *extrapolation*, i.e. given an old timing property value the new value is computed by applying an extrapolation formula. The simplest case is linear extrapolation. For example, if the processor clock rate changes, then the new WCET may be estimated as WCET<sub>new</sub> = WCET<sub>old</sub> \* Clock<sub>old</sub> /

Clock<sub>new</sub>, where Clock is the number of processor cycles per second. For this simple formula it is assumed that the number of processor cycles for reading and writing memory remains the same. Note, that extrapolation is a kind of estimation, so it may be necessary to add a safety margin to the new WCET and to classify it accordingly. One advantage is that extrapolation can be supported by tools.

- Measuring execution times of Solution\_INTEG's components on the new target – this follows a bottom-up approach and requires the availability of the target processor and the possibility of easily porting Solution\_INTEG on the target processor before integration.

- Complete re-computation of the WCET by static analysis of the new function in the environment of Solution\_BOTH. This also requires detailed knowledge about the implementation on the new target.

The methodology does ot give advice on how to update the necessary timing properties; this is subject to specific characteristics of a particular project.

Subtask 2 deals with updating the timing properties of Solution\_EXIST. These timing properties might change in the presence of the integrated design function. Examples of timing properties subject to change are:

- WCET (e.g. due to caching effects, pipelining, etc.)

- Scheduling parameters (e.g. priorities, periods, runnable order, etc.).

- Arbitration of network messages.

### **Analyze Timing Model**

In the task *Analyze Timing Model*, the Solution\_BOTH model is analyzed by means of, for instance, simulation and/or static analysis. This will result in timing property values and metrics relevant for judging the timing behavior of Solution BOTH.

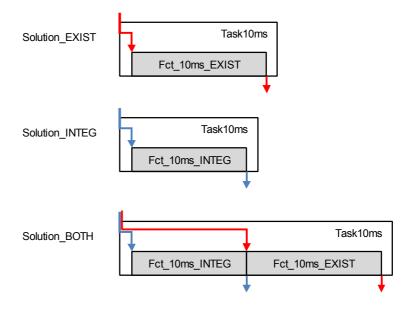

In particular, it is necessary to also re-analyze the timing behavior of components originating from Solution\_EXIST, because after integration some of their timing property values may have changed. For instance, response times (WCRT) may increase due to intercomponent interference from added components (see Figure 14).

Figure 14 - Timing behavior before and after integration

Figure 14 illustrates possible effects due to integration. Both Solution\_EXIST and Solution\_INTEG have functions which are activated with 10ms period. Fct\_10ms\_INTEG has been mapped into the same 10ms task which contains Fct\_10ms\_EXIST. Certain considerations led to the design decision that Fct\_10ms\_INTEG shall be placed at the beginning of the task. Of course, this leads to an increased response time of the 10ms task (and all lower-priority tasks) compared to before the integration. Also the response time of function Fct\_10ms\_EXIST will increase in the depicted scenario.

# Verify Solution against Timing Requirements

The task *Verify Solution against Timing Properties* compares the analysis results for Solution\_BOTH with the requirements.

Besides verifying the timing requirements of the integrated Solution\_INTEG also the timing requirements of the original system Solution\_EXIST, which is now a part of Solution\_BOTH, has to be reverified.

### Specify and Validate Timing Requirements

The scope of the task *Specify and Validate Timing Requirements* is to identify timing requirements for the next lower level of abstraction. These timing requirements refer to event chain segments in the timing model of Solution\_BOTH. The time budgets for each segment must not exceed the specified total budget for the overall event chain. They have to be transformed into requirements for the lower abstraction layer in the next step.

The activities to be done in the task *Specify Timing Requirements* are not specific to this use case. Therefore, this task is not described here in more detail.

### Remark

If the reusable component (Solution\_EXIST) was already applied in other types of vehicles as described in the beginning, then it is likely that not only a *Design*-level solution exists, but also an *Implementation*-level solution, which has to be ported to the new platform.

On the *Implementation* Level similar tasks have to be performed as described for the *Design* Level, i.e. an existing AUTOSAR Solution\_EXIST has to be integrated into an AUTOSAR Solution\_INTEG. Additional complexity results from the re-use of common software components, e.g. for basic software services. Again, the timing properties of both solution parts will persist, but their values may change and must be verified or validated against the original requirements.

### 5.2 Specify timing budgets

#### Problem statement

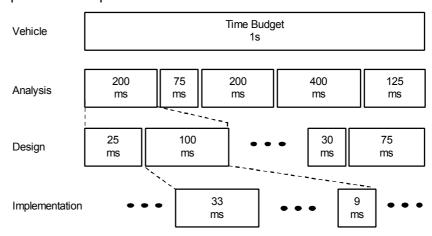

A driver generally has certain expectations on the reactivity of the vehicle he is driving. For example, it would not be acceptable to wait for 5 seconds for the doors to unlock after he has pressed the key. A more acceptable time limit would be 1 second. The main characteristic of this example is that the time limit refers to a stimulus from and to a response to the environment of the system. Such time limits, hereafter called end-to-end delays (or requirements), are specified based on a user's perception with respect to certain functionality.

In a design, the data and control flow paths between a stimulus and a response generally go through several components. Each path delimited by a stimulus and a response that relate to the environment are called end-to-end event chains. The components in the end-to-end event chain are to be implemented by different suppliers or in-house development teams. It therefore has to be clear for each such supplier or team exactly how big portion of the total end-to-end delay is available for the component that they implement.

A similar situation occurs when a control algorithm needs to impose a maximum age on its sensor input data. In that case, an event chain is defined from sensor to the input of the control function. This type of time budgeting and the one mentioned previously are handled in a similar way methodologically, but requires a different use of TADL notation due to the need of a slightly different semantics (reaction vs. age). The following description will not make a clear distinction between these two types of time budgeting.

Following from the above, time budgeting is about dividing an overall end-to-end delay into smaller segments, in order to specify how big portion a component (or subcomponent) in the path between stimulus and response may take.

#### Overview

An end-to-end delay generally originates from either an explicit or implicit user requirement or expectation, or from control performance needs. Other sources of end-to-end delays are legislation, standards or legacy. The methodology described here focuses on how to distribute such an end-to-end latency over the components and subcomponents in the end-to-end event chain.

At the same time with this top-down segmentation of the end-to-end delay, another part of the development project starts with defining hardware, software platforms and other low level details. Legacy functions are also already being introduced. All this means that there is already early in the development process detailed information about the final solution that could be useful when assigning time budgets. Thus, it is beneficial to also introduce a bottom-up flow of timing information for the purpose of time budgeting. This will reduce the number of design iterations. A major issue is how to handle this mix of

bottom-up and top-down information. Figure 15 illustrates the main idea of time budgeting.

For example, on vehicle level, a requirement may postulate that "The doors shall be unlocked not later than 1 second after a valid transponder key has been recognized". This requirement specifies the end-to-end delay that is to be segmented over the end-to-end event chain on the various abstraction levels.

Since the operational level is the lowest abstraction level, time budgeting is not performed at this level. It only serves to feed the bottom-up flow with measured execution data, and to verify that no task execution times in the final implementation exceed the time budgets specified on implementation level.

Figure 15 - The principles of time budgeting

The time budgeting process contains, in addition to the above, clear elements of negotiation between OEMs and suppliers, as well as exchanging timing models between the different parties. For this reason, it is heavily encouraged to combine the time budgeting process with the processes proposed in the use cases Negotiate time budgets and Exchange models.

#### **Definitions**

Before describing the time budgeting methodology, we need to clarify the concepts of time budget influencing property, slack and margin.

A *time budget influencing property* is a property that has the potential to influence the response time of a certain end-to-end event chain, and thereby also the required time budget. The following properties with this potential have been identified:

- Worst-case execution time (WCET)

- Response time

- Communication delay

- Interference time

- Task period

*Slack* is a portion of an end-to-end delay that is not allocated to any budget segment. Thus, there is only one slack per end-to-end delay. Slack is generally not communicated to suppliers, but rather serves as a reserve for interference from other not yet implemented functionality.

*Margin* is a part of a budget segment that is excess to the response time of the corresponding component. There is thus at most one margin per segment. Since margin is part of a budget segment, it is (at least implicitly) communicated to suppliers.

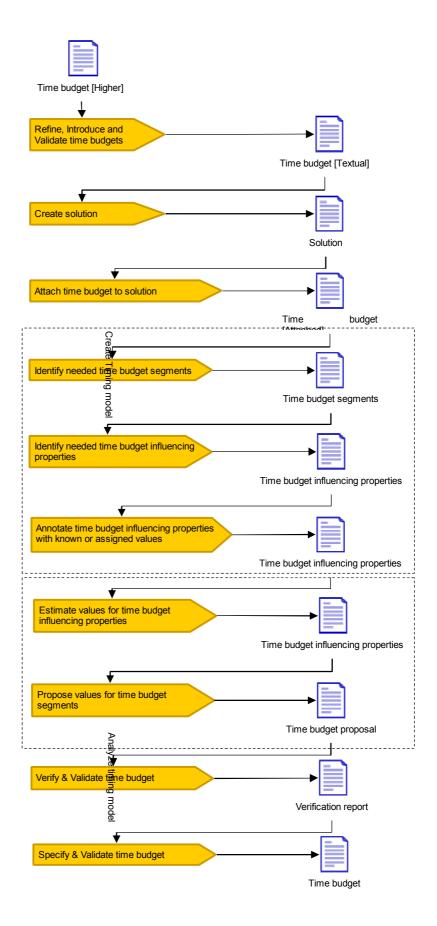

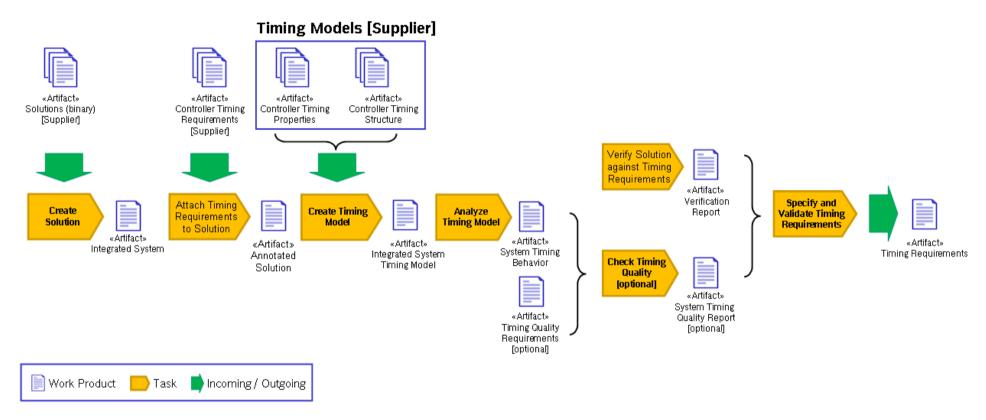

# Mapping to generic methodology

Figure 16 presents the time budgeting process, and how it maps to the GMP presented in Section 3. The *Create timing model* and the *Analyze timing model* tasks have been split into several subtasks each in order to illustrate the activities to be performed in these tasks in more detail. Moreover, the other GMP tasks have been renamed to better reflect their purposes in the context of this use case. The following paragraphs will describe the figure in more detail.

# Refine, Introduce and Validate time budgets

This task translates the time budgets from the immediately higher abstraction level into a textual equivalent on the current abstraction level with an imagined or anticipated solution (or at least main characteristics thereof) in mind. Such textual budget requirement are usually of the form "The Controller shall not take longer time than 50ms from receiving an input to producing an output". The Controller is in this case a known entity from the higher abstraction level, and it is assumed that it will be refined into a distinct set of functions/components at this abstraction level.

#### Create solution

The solution is created as specified in the generic methodology. It should however be emphasized that this solution shall be created while taking the textual time budget requirements into account. This means, for instance, that if the time budget over a series of components is very tight, it may not be appropriate to allocate the components on different ECUs scattered across the vehicle, so that a large portion of the available budget is wasted on communication. Measures must be taken to maximize the probability that the solution meets the time budget requirements. In order to make sound decisions about the distribution of components based on time budgets also information about the amount of interference is needed. This information can, for instance, be derived bottom-up from existing parts of the solution.

Figure 16 - The time budgeting methodology

### Attach time budget to solution